### ADVANCE INFORMATION TO BE ANNOUNCED

#### DESCRIPTION

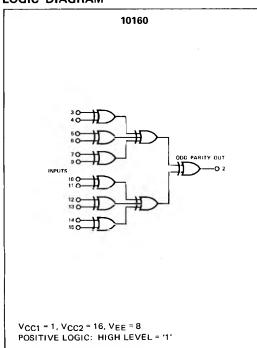

The 10160 is a high performance parity circuit constructed with nine EXCLUSIVE-OR gates in a single package, internally connected to provide odd parity checking or generation.

Input pulldown resistors ensure that the unconnected inputs are pulled to low logic level allowing parity detection and generation for less than 12 bits.

The Output goes high with ODD parity on input pins 3 through 15. (That is, if there are 1,3,5,7,9 or 11 '1's on these inputs).

Expansion for word lengths greater than 12 bits can be achieved by connecting to the carry inputs of the 10170 Parity Circuit or by using 10107 or 10113 EXCLUSIVE-OR gates.

#### LOGIC DIAGRAM

10160 F: -30 to +85°C

12-BIT PARITY | 10160 CHECKER-GENERATOR CIRCUIT |

# DIGITAL 10,000 SERIES ECL

#### **FEATURES**

- HIGH FUNCTIONAL DENSITY ON ONE CHIP REDUCES PACKAGE COUNT AND SAVES SYSTEM POWER

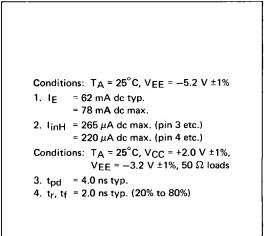

- FAST PROPAGATION DELAY = 4.0 ns TYP

- LOW POWER DISSIPATION = 325 mW/PACKAGE TYPE (NO LOAD)

- HIGH FANOUT CAPABILITY CAN DRIVE 50  $\Omega$  LINES

- HIGH Z INPUTS INTERNAL 50 k $\Omega$  PULLDOWNS

- HIGH IMMUNITY FROM POWER SUPPLY VARIA-TIONS:  $V_{EE} = -5.2 \text{ V} \pm 5\% \text{ RECOMMENDED}$

- OPEN EMITTER LOGIC AND BUSSING CAPABILITY

#### **ELECTRICAL CHARACTERISTICS**

#### **TEMPERATURE RANGE**

• -30 to +85°C Operating Ambient

## PACKAGE TYPE

F: 16-Pin CERDIP