# 54/7493A 54LS/74LS93 DIVIDE-BY-SIXTEEN COUNTER

**DESCRIPTION** — The '93 is a 4-stage ripple counter containing a high speed flip-flop acting as a divide-by-two and three flip-flops connected as a divideby-eight. HIGH signals on the Master Reset (MR) inputs override the clocks and force all outputs to the LOW state.

#### **ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                   | MILITARY GRADE                                                    | PKG  |

|--------------------|-----|--------------------------------------------------------------------|-------------------------------------------------------------------|------|

| PKGS               | Ουτ | $V_{CC} = +5.0 V \pm 5\%,$<br>$T_A = 0^{\circ} C to +70^{\circ} C$ | $V_{CC} = +5.0 V \pm 10\%,$<br>T <sub>A</sub> = -55° C to +125° C | TYPE |

| Plastic<br>DIP (P) | A   | 7493APC, 74LS93PC                                                  |                                                                   | 9A   |

| Ceramic<br>DIP (D) | A   | 7493ADC, 74LS93DC                                                  | 5493ADM, 54LS93DM                                                 | 6A   |

| Flatpak<br>(F)     | A   | 7493AFC, 74LS93FC                                                  | 5493AFM, 54LS93FM                                                 | 31   |

## **INPUT LOADING/FAN-OUT:** See Section 3 for U.L. definitions

| PIN NAMES                         | DESCRIPTION                                       | 54/74 (U.L.)<br>HIGH/LOW | 54/74LS (U.L.)<br>HIGH/LOW |  |

|-----------------------------------|---------------------------------------------------|--------------------------|----------------------------|--|

| CP <sub>0</sub>                   | ÷2 Section Clock Input<br>(Active Falling Edge)   | 2.0/2.0                  | 1.0/1.5                    |  |

| CP <sub>1</sub>                   | ÷5 Section Clock Input<br>(Active Falling Edge)   | 2.0/2.0                  | 1.0/1.0                    |  |

| MR <sub>1</sub> , MR <sub>2</sub> | Asynchronous Master Reset Inputs<br>(Active HIGH) | 1.0/1.0                  | 0.5/0.25                   |  |

| Q <sub>0</sub>                    | ÷2 Section Output*                                | 20/10                    | 10/5.0<br>(2.5)            |  |

| Q1 — Q3                           | ÷8 Section Outputs                                | 20/10                    | 10/5.0<br>(2.5)            |  |

\*The  $Q_0$  output is guaranteed to drive the full rated fan-out plus the  $\overline{CP}_1$  input.

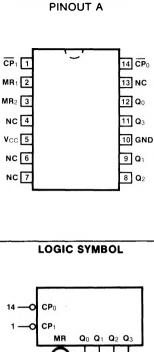

CONNECTION DIAGRAM

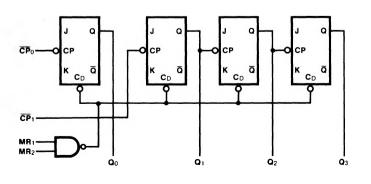

V<sub>CC</sub> = Pin 5 GND = Pin 10 NC = Pins 4, 6, 7, 13 **FUNCTIONAL DESCRIPTION** — The '93 is a 4-bit ripple type binary counter. It consists of four master/slave flip-flops which are internally connected to provide a divide-by-two section and a divide-by-eight section. Each section has a separate clock input which initiates state changes of the counter on the HIGH-to-LOW clock transition. State changes of the Q outputs do not occur simultaneously because of internal ripple delays. Therefore, decoded output signals are subject to decoding spikes and should not be used for clocks or strobes. The Q<sub>0</sub> output of each device is designed and specified to drive the rated fan-out plus the  $\overline{CP_1}$  input of the device. A gated AND asynchronous Master Reset (MR<sub>1</sub>, MR<sub>2</sub>) is provided which overrides the clocks and resets (clears) all the flip-flops. Since the output from the divide-by-two section is not internally connected to the succeeding stages, the devices may be operated in various counting modes.

- A. 4-Bit Ripple Counter The output  $Q_0$  must be externally connected to input  $\overrightarrow{CP}_1$ . The input count pulses are applied to input  $\overrightarrow{CP}_0$ . Simultaneous divisions of 2, 4, 8, and 16 are performed at the  $Q_0$ ,  $Q_1$ ,  $Q_2$ , and  $Q_3$  outputs as shown in the Truth Table.

- B. 3-Bit Ripple Counter The input count pulses are applied to input  $\overrightarrow{CP}_1$ . Simultaneous frequency divisions of 2, 4, and 8 are available at the Q<sub>1</sub>, Q<sub>2</sub>, and Q<sub>3</sub> outputs. Independent use of the first flip-flop is available if the reset function coincides with reset of the 3-bit ripple-through counter.

| RESET<br>INPUTS  |                  | OUTPUTS        |    |                        |    |  |

|------------------|------------------|----------------|----|------------------------|----|--|

| MR1              | MR <sub>2</sub>  | Q <sub>0</sub> | Q1 | Q2                     | Q3 |  |

| H<br>L<br>H<br>L | H<br>H<br>L<br>L | L              | Co | L<br>unt<br>unt<br>unt | L  |  |

| MODE SELECTION | AODE SE | ELEC | TION |

|----------------|---------|------|------|

|----------------|---------|------|------|

|   |      |    |         |       | Î |

|---|------|----|---------|-------|---|

| н | = HI | GH | Voltage | Level |   |

L = LOW Voltage Level

## TRUTH TABLE

|       | (              | DUT | PUTS | 3              |

|-------|----------------|-----|------|----------------|

| COUNT | Q <sub>0</sub> | Q1  | Q2   | Q <sub>3</sub> |

| 0     | L              | L   | L    | L              |

| 1     | н              | L   | L    | L<br>L         |

| 2     | L              | н   | L    | L              |

| 3     | н              | н   | L    | L              |

| 4     | L              | L   | н    | L              |

| 5     | н              | L   | н    | L<br>L<br>L    |

| 6     | L              | н   | н    | L              |

| 7     | н              | н   | н    | L              |

| 8     | L              | L   | L    | н              |

| 9     | н              | L   | L    | н              |

| 10    | L              | н   | L    | н              |

| 11    | н              | н   | L    | н              |

| 12    | L              | L   | н    | н              |

| 13    | н              | L   | н    | н              |

| 14    | L              | н   | н    | H              |

| 15    | н              | н   | н    | н              |

NOTE: Output Q<sub>0</sub> connected to CP<sub>1</sub>.

#### LOGIC DIAGRAM

#### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified) 54/74 54/74LS SYMBOL UNITS CONDITIONS PARAMETER Min Max Min Max Input HIGH Current 0.2 $V_{CC} = Max, V_{IN} = 5.5 V$ Ιн 1.0 mΑ CP0 or CP1 Power Supply Current 39 15 mΑ Vcc = Max Icc. AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ} \text{ C}$ (See Section 3 for waveforms and load configurations) 54/74 54/74LS SYMBOL PARAMETER $C_L = 15 \text{ pF}$ $C_L = 15 \text{ pF}$ UNITS CONDITIONS $R_L = 400 \Omega$ Min Max Min Max Maximum Count Frequency 32 32 fmax MHz Figs. 3-1, 3-9 CPo Input Maximum Count Frequency 16 16 MH<sub>7</sub> Figs. 3-1, 3-9 fmax CP1 Input **t**PLH Propagation Delay 16 16 Figs. 3-1, 3-9 ns CPo to Qo 18 **tPHL** 18 70 70 Propagation Delay **t**PLH ns Figs. 3-1, 3-9 70 **tPHL** CPn to Qa 70 Propagation Delay 16 **t**PLH 16 ns Figs. 3-1, 3-9 CP1 to Q1 21 21 **tPHL** Propagation Delay **t**PLH 32 32 ns Figs. 3-1, 3-9 CP1 to Q2 35 35 **t**PHL Propagation Delay 51 51 **t**PLH Figs. 3-1, 3-9 ns CP1 to Q3 51 51 **tPHL** Propagation Delay **t**PHL 40 40 ns Figs. 3-1, 3-17 MR to Qn

# AC OPERATING REQUIREMENTS: $V_{CC} = +5.0 \text{ V}, \text{ T}_{A} = +25^{\circ} \text{ C}$

| SYMBOL             | PARAMETER                        | 54/74 |     | 54/74LS |     | UNITS | CONDITIONS |

|--------------------|----------------------------------|-------|-----|---------|-----|-------|------------|

|                    |                                  | Min   | Max | Min     | Max | 0     |            |

| t <sub>w</sub> (H) | CP <sub>0</sub> Pulse Width HIGH | 15    |     | 15      |     | ns    | Fig. 3-9   |

| t <sub>w</sub> (H) | CP1 Pulse Width HIGH             | 30    |     | 30      |     | ns    | Fig. 3-9   |

| t <sub>w</sub> (H) | MR Pulse Width HIGH              | 15    | _   | 15      |     | ns    | Fig. 3-17  |

| t <sub>rec</sub>   | Recovery Time, MR to CP          | 25    |     | 25      |     | ns    | Fig. 3-17  |

93