# Philips Components-Signetics

| · · · · · · · · · · · · · · · · · · · |                       |

|---------------------------------------|-----------------------|

| Document No.                          | 853-0130              |

| ECN No.                               | 86487                 |

| Date of Issue                         | November 11, 1986     |

| Status                                | Product Specification |

| Memory Produ                          | ıcts                  |

# 82S181 / 82S181A 8K-bit TTL bipolar PROM

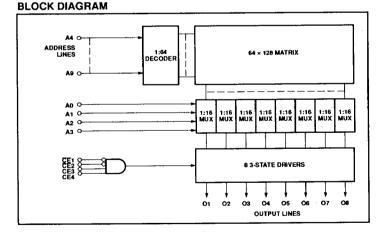

#### DESCRIPTION

The 82S181 and 82S181A are field programmable, which means that custom patterns are immediately available by following the Signetics Generic I fusing procedure. The 82S181 and 82S181A are supplied with all outputs at logical Low. Outputs are programmed to a logic High level at any specified address by fusing the Ni-Cr link matrix.

This device includes on-chip decoding and four Chip Enable inputs for ease of memory expansion. It features 3-State outputs for optimization of word expansion in bused organizations.

Ordering information can be found on the following page.

The 82S181 and 82S181A devices are also processed to military requirements for operation over the military temperature range. For specifications and ordering information consult the Signetics Military Data Handbook.

#### **FEATURES**

- · Address access time:

- N82S181: 70ns max

- N82S181A: 55ns max

- Power dissipation: 76μW/bit typ

- Input loading: −100µA max

- On-chip address decoding

- Four Chip Enable inputs

- Outputs: 3-State

- No separate fusing pins

- Unprogrammed outputs are Low level

- Fully TTL compatible

#### **APPLICATIONS**

- Prototyping/volume production

- Sequential controllers

- Microprogramming

- · Hardwired algorithms

- Control store

- Random logic

- Code conversion

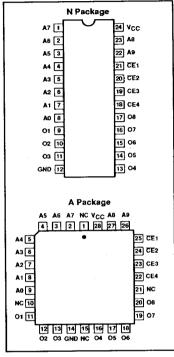

#### PIN CONFIGURATIONS

# 8K-bit TTL bipolar PROM (1024 $\times$ 8)

82S181 / 82S181A

#### ORDERING INFORMATION

| DESCRIPTION                                         | ORDER CODE            |  |  |  |

|-----------------------------------------------------|-----------------------|--|--|--|

| 24-Pin Plastic Dual-In-Line<br>600mil-wide          | N82S181 N, N82S181A N |  |  |  |

| 28-Pin Plastic Leaded Chip Carrier<br>450mil-square | N82S181 A, N82S181A A |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL           | PARAMETER                   | RATING      | UNIT            |  |

|------------------|-----------------------------|-------------|-----------------|--|

| Vcc              | Supply voltage              | +7.0        | V <sub>DC</sub> |  |

| V <sub>IN</sub>  | Input voltage               | +5.5        | V <sub>DC</sub> |  |

| Vo               | Output voltage Off-State    | +5.5        | V <sub>DC</sub> |  |

| T <sub>amb</sub> | Operating temperature range | 0 to +75    | °C              |  |

| T <sub>stq</sub> | Storage temperature range   | -65 to +150 | °C              |  |

# DC ELECTRICAL CHARACTERISTICS

$0^{\circ}C \le T_{amb} \le +75^{\circ}C, 4.75V \le V_{CC} \le 5.25V$

|                 |                            |                                                                 |     | LIMITS                |      |      |

|-----------------|----------------------------|-----------------------------------------------------------------|-----|-----------------------|------|------|

| SYMBOL          | PARAMETER                  | TEST CONDITIONS <sup>1,2</sup>                                  | Min | Alin Typ <sup>3</sup> |      | UNIT |

| Input volt      | age <sup>2</sup>           |                                                                 |     |                       |      |      |

| V <sub>IL</sub> | Low                        |                                                                 |     |                       | 0.8  | ٧    |

| ViH             | High                       |                                                                 | 2.0 |                       |      | ٧    |

| $V_{iC}$        | Clamp                      | I <sub>IN</sub> = -12mA                                         |     | -0.8                  | -1.2 | V    |

| Output vo       | Itage <sup>2</sup>         |                                                                 |     |                       |      |      |

|                 |                            | CE1,2 = Low, CE3,4 = High                                       |     | I                     |      |      |

| VOL             | Low                        | I <sub>OUT</sub> = 9.6mA                                        |     |                       | 0.45 | V    |

| $V_{OH}$        | High                       | $I_{OUT} = -2.0 \text{mA}$                                      | 2.4 | İ                     |      | ٧    |

| Input curi      | ent <sup>1</sup>           |                                                                 |     |                       |      |      |

| I <sub>IL</sub> | Low                        | V <sub>IN</sub> = 0.45V                                         |     |                       | -100 | μА   |

| l <sub>IH</sub> | High                       | V <sub>IN</sub> = 5.5V                                          |     | Ì                     | 40   | μA   |

| Output cu       | rrent <sup>1</sup>         |                                                                 |     |                       |      |      |

| loz             | Hi-Z state                 | CE1,2 = High, CE3,4 = Low, V <sub>OUT</sub> = 5.5V              |     |                       | 40   | μΑ   |

|                 |                            | : CE1,2 = High, CE3,4 = Low, V <sub>OUT</sub> = 0.5V            |     |                       | -40  | μΑ   |

| los             | Short circuit <sup>4</sup> | CE1,2 = Low, CE3,4 = High, V <sub>OUT</sub> = 0V<br>High stored | -15 |                       | -70  | mA   |

| Supply cu       | ırrent <sup>5</sup>        |                                                                 |     |                       |      |      |

| lcc             |                            | V <sub>CC</sub> = 5.25V                                         |     | 125                   | 175  | mA   |

| Capacitar       | nce                        |                                                                 | •   |                       |      |      |

|                 |                            | CE1,2 = High, V <sub>CC</sub> = 5.0V                            |     |                       |      |      |

| CIN             | Input                      | $V_{1N} = 2.0V$                                                 |     | 5                     |      | pF   |

| Caut            | Output                     | V <sub>OUT</sub> = 2.0V                                         | İ   | 8                     |      | pF   |

### NOTES:

- 1. Positive current is defined as into the terminal referenced.

- All voltages with respect to network ground.

Typical values are at V<sub>CC</sub> = 5V, T<sub>amb</sub> = +25°C.

Duration of the short circuit should not exceed 1 second.

- 5. Measured with all inputs grounded and all outputs open.

# 8K-bit TTL bipolar PROM (1024 $\times$ 8)

# 82S181 / 82S181A

#### **AC ELECTRICAL CHARACTERISTICS**

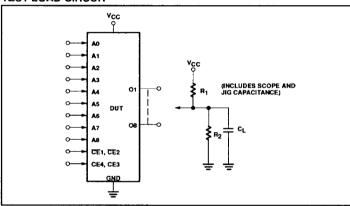

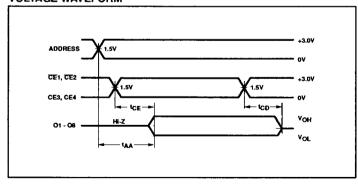

$R_1 = 470\Omega$ ,  $R_2 = 1k\Omega$ ,  $C_L = 30pF$ ,  $0^{\circ}C \le T_{amb} \le +75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$

|                 |                 |        |              | N82S181 |      | N82S181A |     |      |     |      |

|-----------------|-----------------|--------|--------------|---------|------|----------|-----|------|-----|------|

| SYMBOL          | PARAMETER       | то     | FROM         | Min     | Typ¹ | Мах      | Min | Typ1 | Max | UNIT |

| Access tir      | ne <sup>2</sup> |        |              |         |      |          |     |      |     |      |

| t <sub>AA</sub> |                 | Output | Address      |         | 50   | 70       |     | 45   | 55  | ns   |

| t <sub>CE</sub> |                 | Output | Chip Enable  |         | 25   | 40       |     | 25   | 40  | ns   |

| Disable tir     | ne <sup>3</sup> |        |              |         |      |          |     |      |     |      |

| t <sub>CD</sub> |                 | Output | Chip Disable |         | 25   | 40       |     | 25   | 40  | ns   |

#### NOTES:

- 1. Typical values are  $V_{CC}$  = 5V,  $T_{amb}$  = +25°C. 2. Tested at an address cycle time of 1 $\mu$ s. 3. Measured at a delta of 0.5V from Logic Level with  $R_1$  = 750 $\Omega$ ,  $R_2$  = 750 $\Omega$  and  $C_L$  = 5 $\rho$ F.

#### **TEST LOAD CIRCUIT**

### **VOLTAGE WAVEFORM**

November 11, 1986