## 96103

## QUAD BUS TRANSCEIVER

(With Common Enable)

**DESCRIPTION** — Each transceiver contains an open-collector buffer whose output is common to an inverting gate input. When both Enable inputs ( $\overline{E}_1$  and  $\overline{E}_2$ ) are LOW, the buffer is enabled, with its output state determined by its Data (D) input. When either Enable input is HIGH, the buffer is disabled (output OFF) and the bus signal is determined by other circuits connected to the bus. The receiver gate has greater input noise immunity than standard TTL, while its output signal levels are standard TTL. In the power-down condition, the B terminal leakage is limited to 100  $\mu$ A.

**ORDERING CODE:** See Section 9

| PKGS               | PIN<br>OUT | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                                  | PKG<br>TYPE |  |  |

|--------------------|------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------|--|--|

|                    |            | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +75^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C to} + 125^{\circ} \text{ C}$ |             |  |  |

| Plastic<br>DIP (P) | A          | 96103PC                                                                                  |                                                                                                 | 9B          |  |  |

| Ceramic<br>DIP (D) | Α          | 96103DC                                                                                  | 96103DM                                                                                         | 6B          |  |  |

| Flatpak<br>(F)     | Α          | 96103FC                                                                                  | 96103FM                                                                                         | 4L          |  |  |

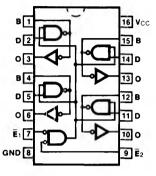

## CONNECTION DIAGRAM PINOUT A

V<sub>CC</sub> = Pin 16 GND = Pin 8

## INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES | DESCRIPTION                | 96XX (U.L.)<br>HIGH/LOW |

|-----------|----------------------------|-------------------------|

| D         | Data Input                 | 1.0/1.0                 |

| Ē1, Ē2    | Enable Inputs (Active LOW) | 1.0/1.0                 |

| В         | Bus Terminal, as Input     | 2.5/0.05                |

|           | as Output                  | OC*/70 mA               |

| 0         | Receiver Output            | 50/12.5                 |

\*OC - Open Collector

$V_{CC} = Max$

| SYMBOL | PARAMETER                            |          | 96XX         |              | UNITS | CONDITIONS                                                                                |

|--------|--------------------------------------|----------|--------------|--------------|-------|-------------------------------------------------------------------------------------------|

|        |                                      |          | Min          | Max          | ]     |                                                                                           |

| VoL    | Output LOW Voltage at B              |          |              | 0.7          | v     | I <sub>OL</sub> = 70 mA, V <sub>IH</sub> = 2.0<br>V <sub>CC</sub> = Min                   |

| VIL    | Input LOW Voltage at D or E          | XC<br>XM |              | 0.8<br>0.7   | V     |                                                                                           |

| Vivia  | Receiver HIGH                        | XC<br>XM | 1.53<br>1.49 |              | ٧     | V <sub>CC</sub> = Min                                                                     |

| Vihr   | Threshold Voltage                    | XC       | 1.7<br>1.84  |              | V     | V <sub>CC</sub> = Max                                                                     |

| N/     | Receiver LOW                         | XC<br>XM |              | 1.3<br>1.21  | ٧     | V <sub>CC</sub> = Min                                                                     |

| VILR   | Threshold Voltage                    | XC       |              | 1.47<br>1.56 | V     | V <sub>CC</sub> = Max                                                                     |

| Іон    | Bus Output HIGH Current              |          |              | 100          | μΑ    | V <sub>CC</sub> = 0 V to Max<br>V <sub>OH</sub> = 4.0 V, V <sub>D</sub> = V <sub>IL</sub> |

| lıL    | Input LOW Current at B               |          |              | -85          | μΑ    | V <sub>OUT</sub> = 0 V, V <sub>CC</sub> = Max<br>V <sub>D</sub> = V <sub>IL</sub>         |

| los    | Output Short Circuit<br>Current at O |          | -18          | -55          | mA    | V <sub>CC</sub> = Max, V <sub>OUT</sub> = 0                                               |

| lcc    | Power Supply Current                 |          |              | 90           | mA    | D input = 4.5 V<br>Vcc = Max                                                              |

AC CHARACTERISTICS:  $V_{CC} = +5.0 \text{ V}$ ,  $T_A = +25^{\circ}\text{C}$  (See Section 3 for waveforms and load configurations)

| SYMBOL       |                             | <b>96XX</b> C <sub>L</sub> = 15 pF |          | UNITS | CONDITIONS                                                                                                    |

|--------------|-----------------------------|------------------------------------|----------|-------|---------------------------------------------------------------------------------------------------------------|

|              | PARAMETER                   |                                    |          |       |                                                                                                               |

|              |                             | Min                                | Max      | 1     |                                                                                                               |

| tPLH<br>tPHL | Propagation Delay           |                                    | 30<br>23 | ns    | $R_L = 91 \Omega$ to Vcc,<br>200 $\Omega$ to Gnd                                                              |

| tPLH<br>tPHL | Propagation Delay<br>D to B |                                    | 25<br>15 | ns    | Figs. 3-4, 3-5                                                                                                |

| tPLH<br>tPHL | Propagation Delay<br>B to O | 10<br>10                           | 30<br>30 | ns    | $R_L = 390 \Omega$ to $V_{CC}$<br>1.6 k $\Omega$ to Gnd, Fig. 3-4                                             |

| tPLH<br>tPHL | Propagation Delay<br>B to O | 10<br>10                           | 35<br>35 | ns    | R <sub>L</sub> = 390 $\Omega$ to V <sub>CC</sub><br>1.6 k $\Omega$ to Gnd<br>C <sub>L</sub> = 50 pF, Fig. 3-4 |