## QUAD DARLINGTON SWITCH

- FOUR NON INVERTING INPUTS WITH ENABLE

- OUTPUT VOLTAGE UP TO 50 V

- OUTPUT CURRENT UP TO 1.8 A

- VERY LOW SATURATION VOLTAGE

- TTL COMPATIBLE INPUTS

- INTEGRAL FAST RECIRCULATION DIODES

## DESCRIPTION

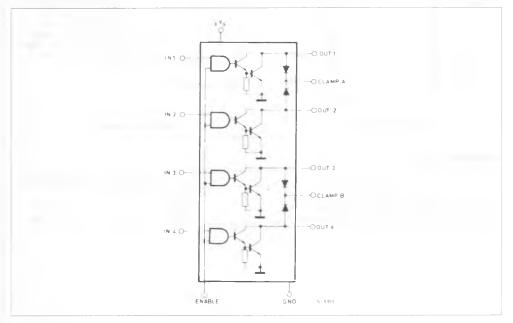

The L6221 monolithic quad darlington switch is designed for high current, high voltage switching applications. Each of the four switches is controlled by a logic input and all four are controlled by a common enable input. All inputs are TTL-compatible for direct connection to logic circuits.

Each switch consists of an open-collector darlington transistor plus a fast diode for switching applications with inductive device loads. The emitters of the four

switches are commoned. Any number of inputs and outputs of the same device may be paralleled.

Two versions are available: the L6221A mounted in a Powerdip 12 + 2 + 2 package and the L6221N mounted in a 15--lead Multiwatt package.

## **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| Vo               | Output Voltage                                                    | 50            | V  |

|------------------|-------------------------------------------------------------------|---------------|----|

| Vs               | Logic Supply Voltage                                              | 7             | V  |

| VIN. VEN         | Input Voltage, Enable Voltage                                     | Vs            |    |

| Ic               | Continuous Collector Current (for each channel)                   | 1.8           | Α  |

| Ic               | Collector Peak Current (repetitive, duty cycle = 10 % ton = 5 ms) | 2.5           | Α  |

| Ic               | Collector Peak Current (non repetitive, t = 10 μs)                | 3.2           | Α  |

| Top              | Operating Temperature Range (junction)                            | - 40 to + 150 | °C |

| T <sub>stg</sub> | Storage Temperature Range                                         | - 55 to + 150 | °C |

| sub              | Output Substrate Current                                          | 350           | mA |

| P <sub>tot</sub> | Total Power Dissipation at T <sub>pins</sub> = 90 °C (powerdip)   | 4.3           | W  |

|                  | at T <sub>case</sub> = 90 °C (multiwatt)                          | 20            | W  |

|                  | at T <sub>amb</sub> = 70 °C (powerdip)                            | 1             | W  |

|                  | at T <sub>amb</sub> = 70 °C (multiwatt)                           | 2.3           | W  |

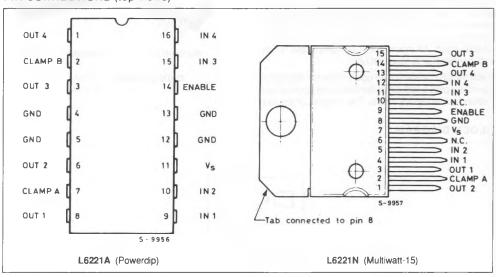

## PIN CONNECTIONS (top views)

## THERMAL DATA

|                        |                                     |     | Powerdip | Multiwatt-15 |

|------------------------|-------------------------------------|-----|----------|--------------|

| R <sub>th j-pins</sub> | Thermal Resistance Junction-pins    | Max | 14 °C/W  | -            |

| Rth j-case             | Thermal Resistance Junction-case    | Max | -        | 3 °C/W       |

| Rth j-amb              | Thermal Resistance Junction-ambient | Max | 80 °C/W  | 35 °C/W      |

|                        |                                     |     |          |              |

## TRUTH TABLE

| Enable | Input | Power Out |  |  |

|--------|-------|-----------|--|--|

| Н      | Н     | ON        |  |  |

| Н      | L     | OFF       |  |  |

| L      | X     | OFF       |  |  |

For each input: H = High level

L = Low level

X = Don't care

## PIN FUNCTIONS (see block diagram)

| Name    | Function                             |  |  |  |

|---------|--------------------------------------|--|--|--|

| IN 1    | Input to Driver 1                    |  |  |  |

| IN 2    | Input to Driver 2                    |  |  |  |

| OUT 1   | Output of Driver 1                   |  |  |  |

| OUT 2   | Output of Driver 2                   |  |  |  |

| CLAMP A | Diode Clamp to Driver 1 and Driver 2 |  |  |  |

| IN 3    | Input to Driver 3                    |  |  |  |

| IN 4    | Input to Driver 4                    |  |  |  |

| OUT 3   | Output of Driver 3                   |  |  |  |

| OUT 4   | Output of Driver 4                   |  |  |  |

| CLAMP B | Diode Clamp to Driver 3 and Driver 4 |  |  |  |

| ENABLE  | Enable Input to All Drivers          |  |  |  |

| Vs      | Logic Supply Voltage                 |  |  |  |

| GND     | Common Ground                        |  |  |  |

# **ELECTRICAL CHARACTERISTICS** Refer to the test circuit to Fig. 1 to Fig. 9 (VS = 5V, Tamb = 25 $^{\circ}$ C unless otherwise specified)

| Symbol                                | Parameter                               | Test Conditions                                               |                                     | Min . | Тур. | Max.  | Unit |

|---------------------------------------|-----------------------------------------|---------------------------------------------------------------|-------------------------------------|-------|------|-------|------|

| Vs                                    | Logic Supply Voltage                    |                                                               |                                     | 4.5   |      | 5.5   | V    |

| Is                                    | Logic Supply Current                    | All Outputs ON I <sub>C</sub> = 0.7 A All Outputs OF          |                                     |       |      | 20    | m A  |

|                                       |                                         |                                                               |                                     |       |      | 20    | m A  |

| V <sub>CE(sus)</sub>                  | Output Sustaining Voltage               | $V_{IN} = V_{IN}L V_{EN} = V_{EN}H$ $I_C = 100$ $mA$          |                                     | 46    |      |       | V    |

| I <sub>CEX</sub>                      | Output Leakage Current                  | $V_{CE} = 50V$ $V_{EN} = V_{EN}H$ $V_{IN} = V_{IN}L$          |                                     |       |      | 1     | mA   |

| V <sub>CE(sat)</sub>                  | Collector Emitter Saturation<br>Voltage | $V_S = 4.5V$ $V_{IN} = V_{IN}H$ $V_{EN} = V_{EN}H$            | I <sub>C</sub> = 0.6 A              |       |      | 1     | V    |

|                                       |                                         |                                                               | I <sub>C</sub> = 1 A                |       |      | 1.2   | V    |

|                                       |                                         |                                                               | I <sub>C</sub> = 1.8 A              |       |      | 1.6   | V    |

|                                       | (one input on ; all others inputs off.) |                                                               |                                     |       |      |       |      |

| V <sub>IN</sub> L, V <sub>EN</sub> L  | Input Low Voltage                       |                                                               |                                     |       |      | 0.8   | V    |

| I <sub>IN</sub> L, I <sub>EN</sub> L  | Input Low Current                       | VIN = VINL                                                    | V <sub>EN</sub> = V <sub>EN</sub> L |       |      | - 100 | μА   |

| V <sub>IN</sub> L, V <sub>EN</sub> H  | Input High Voltage                      |                                                               |                                     | 2.0   |      |       | V    |

| I <sub>IN</sub> H , I <sub>EN</sub> H | Input High Current                      | $V_{IN} = V_{IN}H$                                            | V <sub>EN</sub> = V <sub>EN</sub> H |       |      | ± 10  | μА   |

| R                                     | Clamp Diode Leakage Current             | $V_R = 50 \text{ V}$ $V_{IN} = V_{IN}L$                       | V <sub>EN</sub> = V <sub>EN</sub> H |       |      | 100   | μА   |

| V <sub>F</sub>                        | Clamp Diode Forward Voltage             | I <sub>F</sub> = 1 A                                          |                                     |       |      | 1.6   | V    |

|                                       |                                         | I <sub>F</sub> = 1.8 A                                        |                                     |       |      | 2.0   | V    |

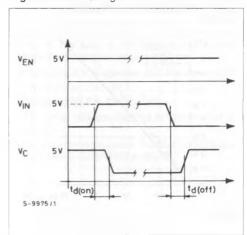

| t <sub>d (on)</sub>                   | Turn on Delay Time                      | V <sub>ρ</sub> = 5V                                           | $R_L = 10\Omega$                    |       |      | 2     | μs   |

| t <sub>d (off)</sub>                  | Turn off Delay Time                     | V <sub>p</sub> = 5V                                           | $R_L = 10\Omega$                    |       |      | 5     | μs   |

| Δls                                   | Logic Supply Current Variation          | V <sub>IN</sub> = 5V<br>I <sub>out</sub> = - 500 r<br>Channel |                                     |       |      | 150   | m A  |

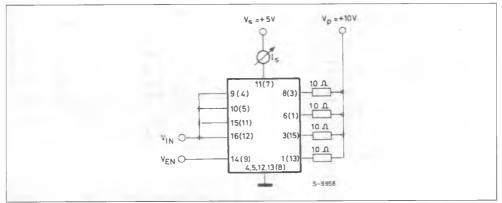

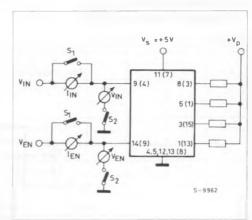

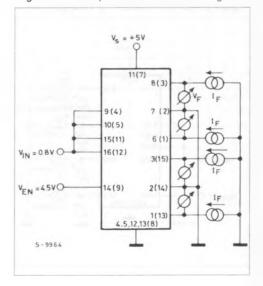

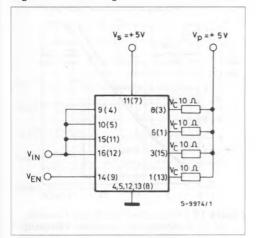

## TEST CIRCUITS

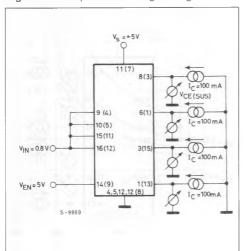

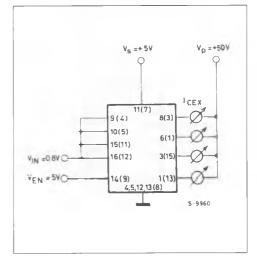

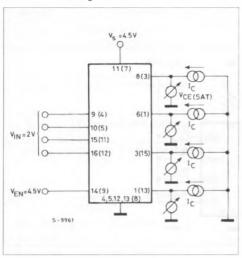

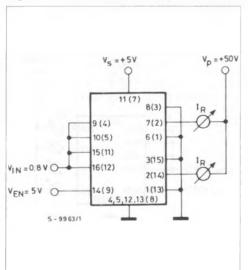

(X) = Referred to Multiwatt package

X = Referred to Powerdip package

Figure 1: Logic supply current.

$S_{el}$  V  $_{IN}$  = 4.5V, V  $_{EN}$  = 0.8V, or V  $_{IN}$  = 0.8V, V  $_{EN}$  = 4.5V, for I  $_S$  (all outputs off)  $S_{el}$  V  $_{IN}$  = 2V, V  $_{EN}$  = 2V, for I  $_S$  (all outputs on)

Figure 2: Output Sustaining Voltage.

Figure 3: Output Leakage Current.

Figure 4 : Collector-emitter Saturation Voltage.

Figure 6 : Clamp Diode Leakage Current.

Figure 5 : Logic Input Characteristics.

$S_{e1} / S_1, \, S_2$  open.  $V_{IN}, \, V_{EN} = 0.8 V$  for  $I_{IN} / L$  ,  $I_{EN} / L$

Set S1. S2 open. VIN. VEN = 2V for In H. IEN H

$S_{e1}$   $S_1$ ,  $S_2$  close.  $V_{IN}$ ,  $V_{EN}$  = 0.8V for  $V_{IN}$  L.  $V_{EN}$  L  $S_{e1}$   $S_1$ ,  $S_2$  close.  $V_{IN}$ ,  $V_{EN}$  = 2V for  $V_{IN}$  H.  $V_{EN}$  H

Figure 7: Clamp Diode Forward Voltage.

Figure 8: Switching Times Test Circuit.

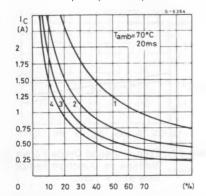

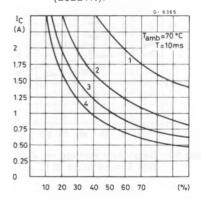

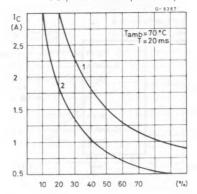

Figure 10: Allowed Peak Collector Current vs. Duty Cycle for 1, 2, 3 or 4 Contemporary Working Outputs (L6221A).

Figure 9: Switching TImes Waveforms.

Figure 11: Allowed Peak Collector Current vs. Duty Cycle for 1, 2, 3 or 4 Contemporary Working Outputs (L6221N).

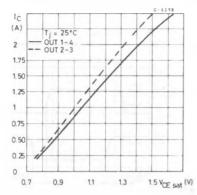

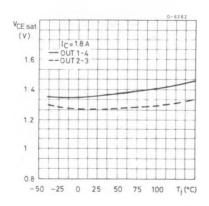

Figure 12 : Collector Saturation Voltage

vs. Collector Current.

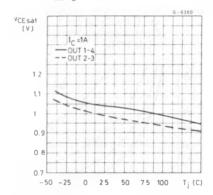

Figure 14: Collector Saturation Voltage vs. Junction Temperature at Ic = 1A.

Figure 16: Saturation Voltage vs. Junction Temperature at IC = 1.8A.

Figure 13: Free-wheeling Diode Forward

Voltage vs. Diode Current.

Figure 15: Free-wheeling Diode Forward

Voltage vs. Junction Temperature at Is = 1A.

Figure 17: Free-wheeling Diode Forward

Voltage vs. Junction Temperature at If = 1.8A.

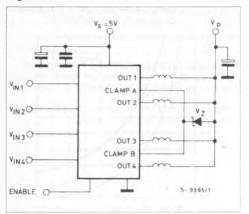

Figure 18.

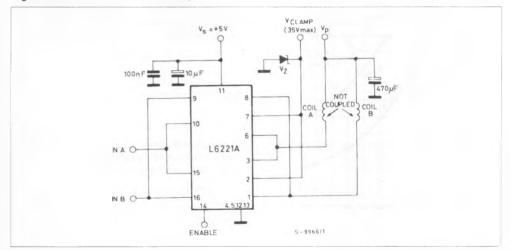

Figure 19: Driver for Solenoids up to 3A.

#### APPLICATION INFORMATION

When inductive loads are driven by L6221 A/N, a zener diode in series with the integral free-wheeling diodes increases the voltage across which energy stored in the load is discharged and therefore speeds the current decay (fig. 18).

For reliability it is suggested that the zener is chosen so that  $V_0 + V_2 < 35 \text{ V}$ .

The reasons for this are two fold:

- The zener voltage changes in temperature and current.

- The instantaneous power must be limited to avoid the reverse second breakdown.

Some care must be taken to ensure that the collectors are placed close together to avoid different current partitioning at turn-off.

We suggest to put in parallel channel 1 and 4 and channel 2 and 3 as shown in figure 19 for the simi-

lar electrical characteristics of the logic section (turnon and turn-off delay time) and the power stages (collector saturation voltage, free-wheeling diode forward voltage).

Figure 20 : Saturation Voltage vs.

Collector Current.

Figure 22: Peak Collector Current vs.

Duty Cycle for 1 or 2 Paralleled

Outputs Driven (L6221N).

Figure 21 : Peak Collector Current vs.

Duty Cycle for 1 or 2 Paralleled

Outputs Driven (L6221A).

#### MOUNTING INSTRUCTION

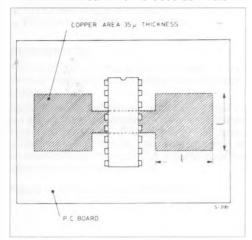

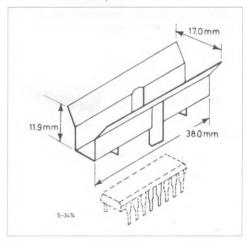

The R<sub>th j-amb</sub> of the L6221A can be reduced by soldering the GND pins to a suitable copper area of the printed circuit board (Fig. 23) or to an external heat-sink (Fig. 24).

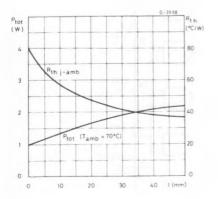

The diagram of figure 25 shows the maximum dissipable power  $P_{tot}$  and the  $R_{th \mid -amb}$  as a function of the side "  $\alpha$ " of two equal square copper areas ha-

Figure 23: Example of P.C. Board Copper

Area Which is Used as Heatsink.

Figure 25: Maximum Dissipable Power and Junction to Ambient Thermal Resistance vs. Side " α".

ving a thickness of  $35\mu$  (1.4 mils). During soldering the pins temperature must not exceed 260  $^{\circ}\text{C}$  and the soldering time must not be longer than 12 seconds.

The external heatsink or printed circuit copper area must be connected to electrical ground.

Figure 24 : External Heatsink Mounting Example.

Figure 26: Maximum Allowable Power Dissipation vs. Ambient Temperature.