Monolithic Linear IC

## LA7286

## VCR Audio Signal Recording and Playback Processor

# SANYO

# Functions

- Equalizer amplifier

- Line amplifier

- · Recording amplifier

- · Recording bias current automatic adjustment circuit

- Ripple filter

- Mute

- ALC

- Recording/playback switch

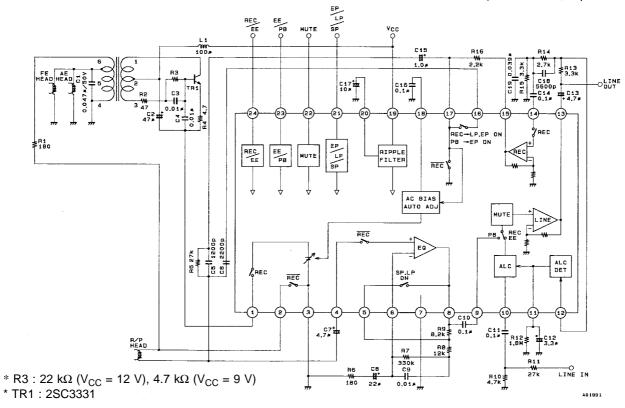

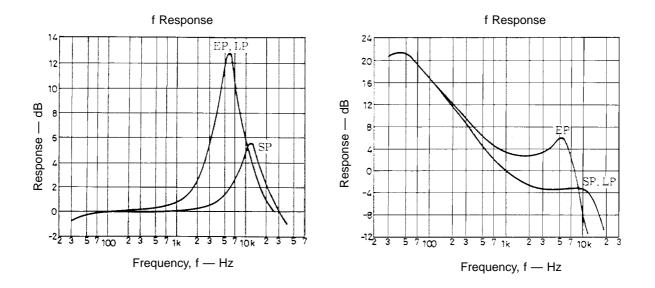

- SP, LP, EP switch

- Tape head switch

## Features

- No adjustment of recording bias current required (due to adoption of automatic adjustment circuit).

- Recording bias oscillation circuit power supply switch on chip.

- Eliminates need for choke coil for recording equalizer.

- Playback amplifier equivalent input noise voltage: 1.0 µVrms.

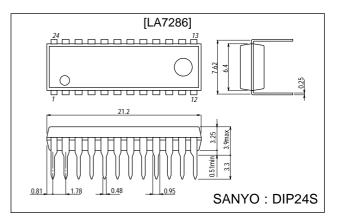

# **Package Dimensions**

unit : mm

#### 3067-DIP24S

- Reduced capacitance (3.3  $\mu$ F) of ALC detection capacitor.

- High withstand voltage head switch on chip.

- Supply voltage: 9 V and 12 V operation.

# **Specifications**

#### Maximum Ratings at Ta = 25 $^{\circ}$ C

| Parameter                   | Symbol              | Conditions  | Ratings     | Unit |

|-----------------------------|---------------------|-------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max |             | 14          | V    |

| Pin 2 input voltages        | V <sub>IN</sub> 2   | DC          | ±65         | Vp-р |

| Pin 2 input current         | I <sub>IN</sub> 2   |             | ±1.5        | mA   |

| Allowable power dissipation | Pdmax               | Ta ≦ 65  °C | 500         | mW   |

| Operating temperature       | Topr                |             | -10 to +65  | °C   |

| Storage temperature         | Tstg                |             | -55 to +150 | °C   |

#### Operating Conditions at Ta = 25 $^{\circ}C$

| Parameter                      | Symbol             | Conditions | Ratings     | Unit |

|--------------------------------|--------------------|------------|-------------|------|

| Recommended supply voltage     | V <sub>CC</sub>    |            | 9, 12       | V    |

| Operating supply voltage range | V <sub>CC</sub> op |            | 8.5 to 12.5 | V    |

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

## Operating Characteristics at Ta = 25 °C, $V_{CC}$ = 12 V, f = 1 kHz, 0 dBV : 1.0 Vrms

| Parameter                         | Symbol                          | Conditions                                            | min  | typ   | max   | Unit  |

|-----------------------------------|---------------------------------|-------------------------------------------------------|------|-------|-------|-------|

| Current consumption (EE)          | I <sub>CCE</sub>                | No signal                                             | 9.5  | 12.0  | 14.5  | mA    |

| Current consumption (PB)          | ICCP                            | No signal                                             | 8.5  | 11.0  | 13.5  | mA    |

| Current consumption (REC)         | ICCR                            | No signal                                             | 8.5  | 10.5  | 12.5  | mA    |

| [Equalizer amplifier]             |                                 |                                                       | 1    |       |       |       |

| Open-circuit voltage gain         | VG <sub>OE</sub>                | $V_0 = -6 \text{ dBV}$                                | 58.4 | 64.4  |       | dB    |

| Equivalent input noise voltage    | V <sub>NIE</sub>                | Rg = 620 $\Omega$ , DIN Audio filter                  |      | 1.0   | 1.8   | μVrms |

| [Line amplifier]                  |                                 |                                                       | 1    |       |       |       |

| Voltage gain (PB input)           | VG <sub>LP</sub>                | $V_0 = -6 \text{ dBV}$                                | 21.0 | 21.5  | 22.0  | dB    |

| Voltage gain (LINE input)         | VG <sub>LR</sub>                | $V_0 = -6 \text{ dBV}$                                | 21.0 | 21.5  | 22.0  | dB    |

| Total harmonic distortion         | THDL                            | $V_0 = -6 \text{ dBV}$                                |      | 0.05  | 0.3   | %     |

| Output noise voltage              | V <sub>NOL</sub>                | $Rg = 1 k\Omega$ , DIN Audio filter                   |      | -80.0 | -74.0 | dBV   |

| Maximum output voltage            | VOML                            | THD = 1%                                              | 1.7  | 2.5   |       | Vrms  |

| Output voltage when ALC is on     | V <sub>OA</sub>                 | $V_{IN} = -26 \text{ dBV}$                            | -7.0 | -6.0  | -5.0  | dBV   |

| ALC effect                        | ALC                             | $V_{IN} = -26 \text{ dBV to } -6 \text{ dBV}$         |      | 1     | 3     | dB    |

| Distortion when ALC is on         | THDA                            | $V_{IN} = -26 \text{ dBV}$                            |      | 0.05  | 0.6   | %     |

| [Recording amplifier ]            |                                 |                                                       |      |       |       |       |

| Voltage gain                      | VG <sub>CR</sub>                | $V_0 = -6 \text{ dBV}$                                | 13.5 | 14.0  | 14.5  | dB    |

| Total harmonic distortion         | THD <sub>R</sub>                | $V_0 = -6 \text{ dBV}$                                |      | 0.05  | 0.3   | %     |

| Maximum output voltage            | VOMR                            | THD = 1%                                              | 1.7  | 2.5   |       | Vrms  |

| [Mute circuit]                    |                                 |                                                       |      |       |       |       |

| On voltage                        | V <sub>MON</sub>                | Pin 22 DC voltage                                     | 2.5  |       | 6.0   | V     |

| Off voltage                       | V <sub>MOFF</sub>               | Pin 22 DC voltage                                     | 0    |       | 1.5   | V     |

| Mute attenuation (PB, EE)         | M <sub>P</sub> , M <sub>E</sub> |                                                       | 80   | 90    |       | dB    |

| [EP, LP, SP switch circuit]       |                                 |                                                       | 1    |       |       |       |

| EP mode hold voltage              | V <sub>EE</sub>                 | Pin 21 DC voltage                                     | 3.6  |       | 6.0   | V     |

| LP mode hold voltage              | V <sub>EL</sub>                 | Pin 21 DC voltage                                     | 1.8  |       | 2.6   | V     |

| SP mode hold voltage              | V <sub>ES</sub>                 | Pin 21 DC voltage                                     | 0    |       | 1     | V     |

| [EE, PB switch circuit]           |                                 |                                                       |      |       |       |       |

| EE mode hold voltage              | $V_{LL}$                        | Pin 23 DC voltage                                     | 3    |       | 6     | V     |

| PB mode hold voltage              | V <sub>LP</sub>                 | Pin 23 DC voltage                                     | 0    |       | 1     | V     |

| [REC, EE switch circuit]          |                                 | •                                                     |      | •     | •     |       |

| REC mode hold voltage             | V <sub>RR</sub>                 | Pin 24 DC voltage                                     | 3    |       | 6     | V     |

| EE mode hold voltage              | V <sub>RE</sub>                 | Pin 24 DC voltage                                     | 0    |       | 1     | V     |

| [Switch]                          |                                 | •                                                     |      | •     |       |       |

| Pin 2 on resistance               | R <sub>ON</sub> 2               | 12 = ±1 mA                                            |      | 10    | 25    | Ω     |

| Pin 2 input voltage               | V <sub>IN</sub> 2               | Ta = 65 °C, f = 80 kHz (sin), I <sub>LK</sub> = 10 μA |      |       | ±45   | V     |

| [Recording bias current automatic | adjustment o                    | circuit]                                              |      | •     | •     |       |

| Recording bias current            | I <sub>B</sub>                  | The conditions for using each head assume the         | 220  | 245   | 270   | μA    |

| Pin 1 output control range        | V <sub>CTL</sub>                | specifications shown below.                           | 2.5  | 4.0   | 6.0   | V     |

#### **Head Coil Specifications**

(1) Application circuit 1 (erase head series type)

| • R/P Head                  | 58 kΩ (typ) | +15% | (f = 70 kHz) |

|-----------------------------|-------------|------|--------------|

|                             |             | -15% |              |

| <ul> <li>AE Head</li> </ul> | 34 Ω (typ)  | +25% | (f = 70 kHz) |

|                             |             | -25% |              |

| • FE Head                   | 80 Ω (typ)  | +20% | (f = 70 kHz) |

|                             |             | -10% |              |

• OSC Coil: Model name 7QM3, Prototype No. C-14290, Tokyo Parts Ind. Co., Ltd. Tel = 0270-25-1191

| STI | _              | Γ     | ]        |                            | ١   |

|-----|----------------|-------|----------|----------------------------|-----|

|     | 3.<br>2-<br>1- | 00000 | (000000) | (4)<br>(5)<br><b>-</b> (6) |     |

|     |                |       |          |                            | ST2 |

| Pin No.               | 3 to 2    | 2 to 1       | 6 to 5       | 5 to 4       |

|-----------------------|-----------|--------------|--------------|--------------|

| Wire type             | 2UEW 0.09 | $\leftarrow$ | $\leftarrow$ | $\leftarrow$ |

| Total number of coils | 32T       | 20T          | 180T         | 25T          |

(2) Application circuit 2 (erase head parallel type)

| • R/P Head | 58 k $\Omega$ (typ) | +10%                | $(f = 70kH_z)$ |

|------------|---------------------|---------------------|----------------|

| • AE Head  | 180 Ω (typ)         | -20%<br>+25%<br>-5% | $(f = 70kH_z)$ |

| • FE Head  | 80 $\Omega$ (typ)   | -5%<br>+20%<br>-20% | $(f = 70kH_z)$ |

• OSC Coil:Model name 7QM3, Prototype No. C-14284, Tokyo Parts Ind. Co., Ltd.

| ST1 ST2 |                       |           |              |              |              |

|---------|-----------------------|-----------|--------------|--------------|--------------|

|         | Pin No.               | 3 to 2    | 2 to 1       | 4 to 5       | 5 to 6       |

|         | Wire type             | 2UEW 0.10 | $\leftarrow$ | $\leftarrow$ | $\leftarrow$ |

|         | Total number of coils | 15T       | 25T          | 110T         | 30T          |

|         |                       |           |              |              |              |

\* The head specifications are as agreed upon by Alps Electric and Sanyo.

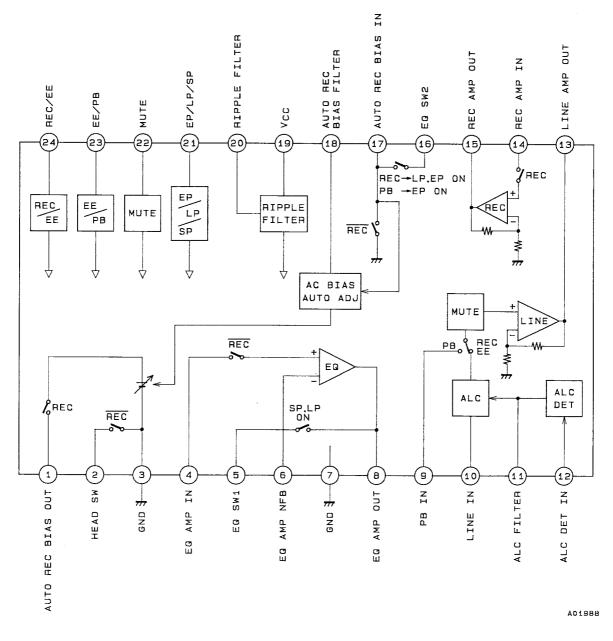

#### **Block Diagram**

## Switch Operation Table

| Test item (symbol)                                     | SW1 | SW2 | SW3 | SW4 | SW5 | SW6 | VM  | VP  | V <sub>R</sub> | Input             | Measure:         |

|--------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|----------------|-------------------|------------------|

| I <sub>CCE</sub>                                       | 2   | 1   | 3   | 2   | 2   | 1   | GND | 5 V | GND            | —                 | Ι <sub>Ο</sub>   |

| I <sub>CCP</sub>                                       | 2   | 1   | 3   | 2   | 2   | 1   | GND | GND | GND            | —                 | Ι <sub>Ο</sub>   |

| I <sub>CCR</sub>                                       | 2   | 1   | 3   | 2   | 2   | 1   | GND | 5 V | 5 V            | —                 | Ι <sub>Ο</sub>   |

| VG <sub>OE</sub>                                       | 1   | 2   | 3   | 2   | 2   | 1   | GND | GND | GND            | V <sub>IN</sub> 1 | V <sub>O</sub> 1 |

| V <sub>INE</sub>                                       | 2   | 1   | 3   | 2   | 2   | 1   | GND | GND | GND            | —                 | V <sub>O</sub> 1 |

| VG <sub>LP</sub> , THD <sub>L</sub> , V <sub>MOL</sub> | 2   | 1   | 2   | 2   | 2   | 1   | GND | GND | GND            | V <sub>IN</sub> 2 | V <sub>O</sub> 2 |

| VG <sub>LR</sub>                                       | 2   | 1   | 3   | 1   | 2   | 1   | GND | 5 V | GND            | V <sub>IN</sub> 3 | V <sub>O</sub> 2 |

| V <sub>ONL</sub>                                       | 2   | 1   | 3   | 2   | 2   | 1   | GND | 5 V | GND            | —                 | V <sub>O</sub> 2 |

| V <sub>OA</sub> , ALC, THD <sub>A</sub>                | 2   | 1   | 3   | 1   | 1   | 1   | GND | 5 V | GND            | V <sub>IN</sub> 3 | V <sub>O</sub> 2 |

| VG <sub>R</sub> , THD <sub>R</sub> , V <sub>MOR</sub>  | 2   | 1   | 3   | 2   | 2   | 1   | GND | 5 V | 5 V            | V <sub>IN</sub> 4 | V <sub>O</sub> 3 |

| MP                                                     | 1   | 1   | 1   | 2   | 2   | 1   | 5 V | GND | GND            | V <sub>IN</sub> 1 | V <sub>O</sub> 2 |

| M <sub>E</sub>                                         | 2   | 1   | 3   | 1   | 2   | 1   | 5 V | 5 V | GND            | V <sub>IN</sub> 3 | V <sub>O</sub> 2 |

| V <sub>BIAS</sub>                                      | 2   | 1   | 3   | 2   | 2   | 2   | GND | 5 V | 5 V            | —                 | V <sub>O</sub> 4 |

| V <sub>CTL</sub>                                       | 2   | 1   | 3   | 2   | 2   | 2   | GND | 5 V | 5 V            | _                 | V1               |

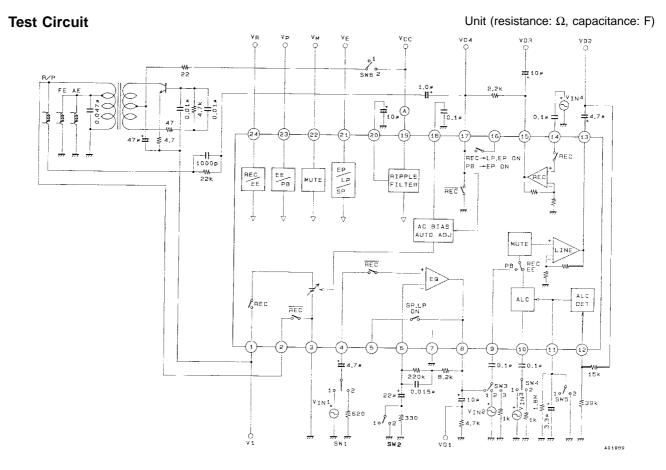

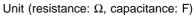

#### Sample Application Circuit : Erase head series type

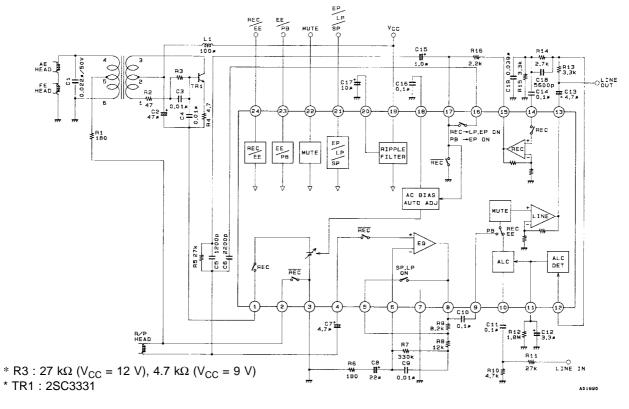

#### Sample Application Circuit : Erase head parallel type

Unit (resistance: Ω, capacitance: F)

#### **Pin Functions**

|         | ns                                            | Unit (resistance: Ω)                                                          |                                                                                                                                                                                                     |  |  |  |  |

|---------|-----------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin No. | Function name                                 | Internal circuit for pin                                                      | Description of function                                                                                                                                                                             |  |  |  |  |

| 1       | Recording bias<br>automatic control<br>output | 27k<br>5.8k<br>1<br>401992                                                    | EE, PB $\rightarrow$ off<br>REC $\rightarrow$ control voltage                                                                                                                                       |  |  |  |  |

| 2       | Head switch<br>(high withstand<br>voltage)    |                                                                               | $\begin{array}{l} EE, PB \rightarrow on \\ REC \rightarrow off \\ On resistance \rightarrow 10 \ \Omega \ (typ) \\ Withstand voltage when off \rightarrow \pm 45 \ V \\ (f = 80 \ KHz) \end{array}$ |  |  |  |  |

| 3       | GND                                           |                                                                               | GND for pin 2 head switch and<br>Equalizer Amplifier only                                                                                                                                           |  |  |  |  |

| 4       | EQ AMP input                                  | VREF<br>120K<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 | Input impedance for playback signal input from head $\rightarrow$ 120 k $\Omega$ (typ)                                                                                                              |  |  |  |  |

| 5       | EQ switch 1                                   |                                                                               | Switches the Playback Equalizer<br>Amplifier high-region frequency<br>voltage gain.<br>LP, SP $\rightarrow$ on<br>EP $\rightarrow$ off<br>On resistance $\rightarrow$ 20 $\Omega$ (typ)             |  |  |  |  |

| 6       | EQ AMP NFB                                    | 6                                                                             | Equalizer Amplifier negative<br>feedback pin                                                                                                                                                        |  |  |  |  |

| 7       | GND                                           |                                                                               | GND for all circuit blocks except the<br>pin 2 head switch and Equalizer<br>Amplifier                                                                                                               |  |  |  |  |

Continued on next page.

Continued from preceding page.

Pin No. Function name Internal circuit for pin Description of function 5 EQ AMP output 8 Output impedance  $\rightarrow$  50 $\Omega$  (typ) A01995 VREF Λ Inputs the playback signal from the Equalizer Amplifier. Because the 120k 🛓 input impedance is as high as 120 9 LINE AMP PB input  $k\Omega$ , a 0.1 µF ceramic capacitor can 9 be used for the coupling capacitor on pin 9. A01997 Inputs EE and REC signals. VREF Rí בם≼ 120k 🛓 AC1999 10 LINE AMP LINE input The reference input is set by (10 resistors R1 and R2. The amplifier gain is fixed at 21.5 dB. In addition, because the input impedance is as high as 120 k $\Omega$ , a 0.1  $\mu$ F ceramic A01998 capacitor can be used for the coupling capacitor on pin 10. \$200 Wave detection is performed when connected to GND through a (11 ALC FILTER 11 capacitor. In addition, the attack and Ź2k recovery time is set by the C and R time constants. A02000 w R 1 ŻR2 ALC input wave 12 detection A02002 Inputs the Line Amplifier output signal. The ALC level is set by the resistors R1 and R2. A02001

Unit (resistance:  $\Omega$ )

Continued on next page.

Unit (resistance:  $\Omega$ )

Continued from preceding page.

Pin No. Function name Internal circuit for pin Description of function (13) 13 LINE AMP output Output inpedance  $\rightarrow$  50  $\Omega$  (typ) A02003 Inputs the recording signal from Line Amplifier. VBEF .A.Ы R1 120k ≸ (14) **REC AMP input** 14 A02005 The recording current is set by the resistors R1 and R2. In addition, because the input impedance is as high as 120 kΩ, a 0.1  $\mu\text{F}$  ceramic A02004 capacitor can be used for the coupling capacitor on pin 14. (15 15 **REC AMP output** Output impedance  $\rightarrow$  50  $\Omega$  (typ) A02005 Switches the high-region peaking frequency during recording and playback. REC PB 17 16 16 EQ switch 2 EP On On LP On Off SP Off Off A02007 On resistance  $\rightarrow$  30  $\Omega$  (typ) (17 IΒ ≷ Recording bias EE, PB  $\rightarrow$  on 17 automatic control  $\mathsf{REC}\to\mathsf{off}$ input and PB switch. On resistance  $\rightarrow$  20  $\Omega$  (typ) 4 VREF A02008

Continued on next page.

Continued from preceding page.

Unit (resistance:  $\Omega$ ) Pin No. Internal circuit for pin Function name Description of function (18) 4 Wave detection is performed when Recording bias 18 connected to GND through a automatic control filter Š capacitor. 402009  $V_{CC} max = 14 V$  $V_{CC} = 8.5 V to 12.5 V$ 19 Supply voltage (V<sub>CC</sub>) Power supply Vcc of each (19) circuit block Ripple rejection is performed when Ripple filter connected to GND through an 20 Ż 43k electrolytic capacitor for the filter. Ż1.5k (20) A02010 When the voltage on pin 21 is 3.6 V to 6.0 V: EP; when 1.8 V to 2.6 V: LP; 10 K when 0 V to 1.0 V: SP Switch On Pin Number EP/LP/SP Control ≸100k 21 REC PB 16 EP 16 5 LP 16, 5 A02011 SP 5 5 10k (22) -NM When the voltage on 1004 22 **MUTE** Control pin 22 is 2.5 V to 6.0 V: MUTE on; when 0 V to 1.5 V: MUTE off A02012 10k ~~ When the voltage on \$100 **EE/PB** Control pin 23 is 3.0 V to 6.0 V: EE; 23 when 0 V to 1.0 V: PB 402013 10k When the voltage on -114 pin 24 is 3.0 V to 6.0 V: REC; when 0V to 1.0 V: EE \$100k **REC/EE** Control 24 However, REC mode is entered only when the voltage on pin 23 is 3.0 V to 6.0 V. A02014

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products(including technical data,services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only ; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of May, 1995. Specifications and information herein are subject to change without notice.