# **PAL/SECAM Discrimination Circuit for VHS VCRs**

### **Overview**

The LA7357 can be used as a PAL/SECAM discrimination IC. Since no ceramic resonator or tank circuit is required, only a small number of external components are used, and the LA7357 can contribute to reduced mounting areas and lower system costs.

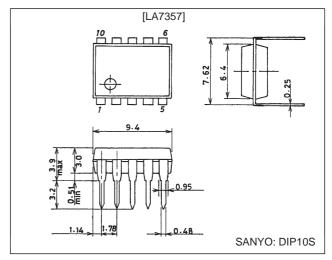

## **Package Dimension**

unit: mm

#### 3098B-DIP10S

## **Specifications**

Maximum Ratings at  $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions | Ratings     | Unit |

|-----------------------------|---------------------|------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max |            | 7.0         | V    |

| Allowable power dissipation | Pd max              | Ta ≤ 65 °C | 120         | mW   |

| Operating temperature       | Topr                |            | -10 to +65  | °C   |

| Storage temperature         | Tstg                |            | -40 to +125 | °C   |

### Operating Conditions at $Ta = 25^{\circ}C$

| Parameter               | Symbol             | Conditions | Ratings    | Unit |

|-------------------------|--------------------|------------|------------|------|

| Supply voltage          | V <sub>CC</sub>    |            | 5.0        | V    |

| Operating voltage range | V <sub>CC</sub> op |            | 4.8 to 5.5 | V    |

## LA7357

# Operating Characteristics at $Ta=25^{\circ}C,\,V_{CC}$ = 5~V

| Parameter                                | Cumbal            | Conditions                                                                                                                                                  |             | Unit |      |        |  |

|------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|------|--------|--|

| Parameter                                | Symbol            | Conditions                                                                                                                                                  | min typ max |      | max  | _ Unit |  |

| Ourse et design                          | I <sub>CC</sub> 1 | Pin 5 = ground, pin 7 influx current: T4 output                                                                                                             | 7.0         | 10.0 | 13.0 | mA     |  |

| Current drain                            | I <sub>CC</sub> 2 | Pin 5 = V <sub>CC</sub> , pin 7 influx current: T4 output                                                                                                   | 7.5         | 10.5 | 13.5 | mA     |  |

| BGP threshold level                      | втн               | The pin 5 voltage when the pin 2 output appears when slowly raising the voltage applied to pin 5 from 0 V. The input signal should be 300 mVp-p: T2 output  | 2.2         | 2.5  | 2.8  | V      |  |

| SYNC threshold level                     | STH               | The pin 5 voltage when the pin 2 output appears when slowly lowering the voltage applied to pin 5 from 5 V. The input signal should be 300 mVp-p: T2 output | 0.6         | 0.8  | 1.0  | V      |  |

| Input limiter amplifier gain             | LIMG              | Stipulated as the output ratio when a<br>10 mVp-p amplitude sine wave is input to<br>pin 1: T2 output                                                       | 9           | 12   | 15   | dB     |  |

| Input limiter amplifier level            | LIMD              | Measure the output amplitude when a 300 mVp-p amplitude sine wave is input to pin 1: T2 output                                                              | 150         | 190  | 230  | mVp-p  |  |

| Comparator hysteresis high-level voltage | Comp H            | The V1 level when T1 switches from low to high when slowly raising V1 from 0 V: T1 output                                                                   | 2.7         | 3.0  | 3.3  | V      |  |

| Comparator hysteresis low-level voltage  | Comp L            | The V1 level when T1 switches from high to low when slowly lowering V1 from 5 V: T1 output                                                                  | 2.0         | 2.3  | 2.6  | V      |  |

| DET-OUT output high-level voltage        | DETH              | With a 2-kΩ load: T1 output                                                                                                                                 | 3.6         | 4.0  | 4.4  | V      |  |

| DET-OUT output low-level voltage         | DETL              | With a 2-kΩ load: T1 output                                                                                                                                 | 0           | 0.2  | 0.4  | V      |  |

# **Switching Conditions**

|                   | Input signal |            | Input pulse |           | Applied voltage   |                   | Switch states |     |     |     |     |

|-------------------|--------------|------------|-------------|-----------|-------------------|-------------------|---------------|-----|-----|-----|-----|

| Symbol            | S1           | S2         | S3          | S4        | V1                | V2                | SW1           | SW2 | SW3 | SW4 | SW5 |

| I <sub>CC</sub> 1 | No signal    | No signal  | 0 V         | 0 V       |                   |                   | Off           | Off | Off | Off | Off |

| I <sub>CC</sub> 2 | No signal    | No signal  | 5 V         | 5 V       |                   |                   | Off           | Off | Off | Off | Off |

| BTH               | Sig.1        | No signal1 | 0 V         | 0 V       |                   | Variable DC level | On            | Off | On  | Off | Off |

| STH               | No signal    | Sig.1      | 0 V         | 0 V       |                   | Variable DC level | On            | Off | On  | Off | Off |

| LIMG              | Sig.1        | No signal  | 5 V         | 0 V       |                   |                   | On            | Off | Off | Off | Off |

| LIMD              | Sig.1        | No signal  | 5 V         | 0 V       |                   |                   | On            | Off | Off | Off | On  |

| Comp H            | No signal    | No signal  | No signal   | No signal | Variable DC level |                   | Off           | On  | Off | Off | On  |

| Comp L            | No signal    | No signal  | No signal   | No signal | Variable DC level |                   | Off           | On  | Off | Off | On  |

| DETH              | Sig.2        | Sig.1      | P2          | P1        |                   |                   | Off           | Off | Off | Off | On  |

| DETL              | Sig.3        | Sig.1      | P2          | P1        |                   |                   | Off           | Off | Off | Off | On  |

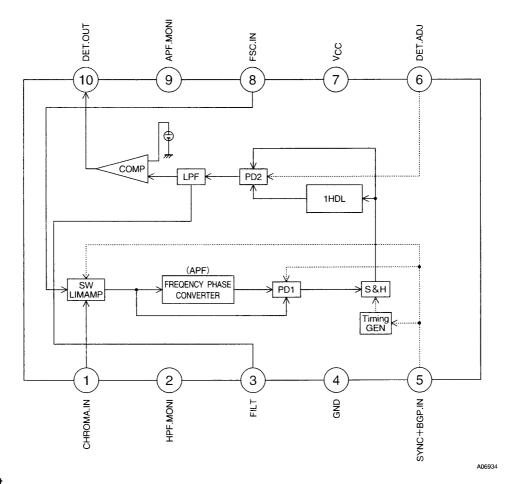

## **Block Diagram**

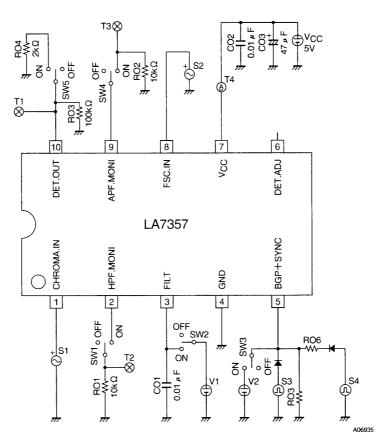

## **Test Circuit**

## **Pin Functions**

| Pin No. | Pin             | Pin Functions                                                                                                                                                                                                 | Equivalent circuit                                |

|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1       | CHROMA-IN       | Chrominance signal input. This pin can handle burst (or unmodulated carrier for SECAM input) signal amplitudes of between 50 and 800 mVp-p.                                                                   | 10pF<br>10pF<br>25kΩ \$ 1kΩ<br>10pF<br>100 μ A)   |

| 2       | HPF.MONI        | High-pass filter output monitor     To avoid interference between pin 1 and pin 3, this pin should be connected to V <sub>CC</sub> during normal operation.                                                   | (100 μ A)<br>200 Ω ₹<br>A06937                    |

| 3       | FILTER          | Phase comparator output This signal is smoothed with an external capacitor. The smoothed level will be: 2.0 V or lower for PAL 3.5 V or higher for SECAM or MESECAM.                                          | 300Ω 4kΩ 34kΩ A06938                              |

| 4       | GND             |                                                                                                                                                                                                               |                                                   |

| 5       | SYNC+BGP        | • BGP + SYNC input The input level is a 1.0- to 2.0-V rising pulse (                                                                                                                                          | 10kΩ \$\frac{1}{2}\$10kΩ 10kΩ 10kΩ 10kΩ 10kΩ 10kΩ |

| 6       | DET-ADJ         | Discrimination sensitivity adjustment pin     The discrimination is shifted towards PAL as the pin voltage is increased, and towards SECAM as the pin voltage is lowered.     This pin is normally left open. | 6<br>50kΩ<br>1kΩ<br>2.5V<br>(70 μ A) A06940       |

| 7       | V <sub>CC</sub> |                                                                                                                                                                                                               |                                                   |

Continued on next page.

Continued from preceding page.

| Pin No. | Pin      | Pin Functions                                                                                                                               | Equivalent circuit                                                  |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 8       | FSC-IN   | • PAL fsc (4.43 MHZ) input This pin can handle inputs with amplitude between about 300 and 800 mVp-p.                                       | 8<br>3kΩ ₹ 3kΩ<br>10pF<br>25kΩ ₹ 25kΩ<br>2.5V 8<br>(100 μ A) A06941 |

| 9       | AFP.MONI | APF output monitor     This pin must be connected to V <sub>CC</sub> to prevent interference between pins 8 and 10.                         | 9<br>200Ω<br>(50 μ A)<br>A06942                                     |

| 10      | DET-OUT  | Discrimination output     This pin outputs a high level (4.2 V) for SECAM or MESECAM inputs, and a low level (close to 0 V) for PAL inputs. | ₹18kΩ ₹200Ω<br>10)                                                  |

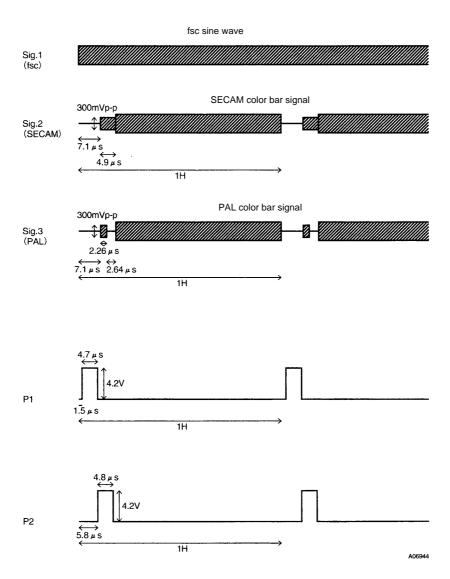

### **Test Input Signals and Pulses**

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of July, 1997. Specifications and information herein are subject to change without notice.