# LC73701M

# **Serial Interface Dialler**

# Overview

The LC73701M is a DTMP/pulse output dual-system dialer CMOS LSI for use in push-button telephones. It provides an on-chip serial interface and operates under the control of data sent over that serial interface. The LC73701M can be easily controlled by the system CPU using this dedicated interface.

# **Functions**

- Functions as a dialer that is controlled over a serial interface.

- The built-in oscillator circuit ( $f_{OSC} = 4.19$  MHz) can use either a crystal oscillator or a ceramic resonator as its oscillator element.

- The adoption of a high-precision (±0.04%) DTMF signal frequency divider circuit allows a ceramic resonator to be used as the oscillator element.

- The buffer memory can store up to 32 digits of 5-bit data.

- Mode change and pause commands can also be stored as data in the buffer memory.

- Pauses can be inserted automatically on mode changes (auto-pause).

- A pause can be cancelled during that pause.

- The mode change function supports changing from pulse to tone (single direction).

- Generates all 16 DTMF signals.

- The pulse dialer output can be turned on or off arbitrarily.

- The pulse dialer output circuit can be selected to be either an n-channel open drain or a complementary circuit.

- The pulse dialer muting function can be turned on or off arbitrarily.

- A redial function is provided.

- Flash operation is supported. (Data can be received during flash operation.)

- The flash time can be switched to be either 277 or 707 ms.

- The pause time can be switched to be either 2 or 4 seconds.

- Hooking pause operation is supported. (1.2 s or 801 ms)

- The dial pulse rate can be specified to be either 10 pps or 20 pps.

- The dial pulse make ratio can be specified to be either 33 or 39%.

- Wide operating voltage range

Pulse mode:  $V_{DD} = 1.5$  to 5.5 V DTMF mode:  $V_{DD} = 2.0$  to 5.5 V

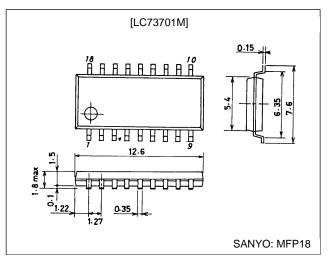

# **Package Dimensions**

unit: mm

### 3095-MFP18

## SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

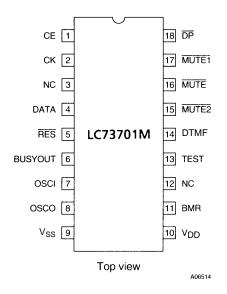

# **Pin Assignment**

#### **Pin Functions**

| Pin No. | Pin             | I/O | Pin function                                                                                                                                                     |

|---------|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

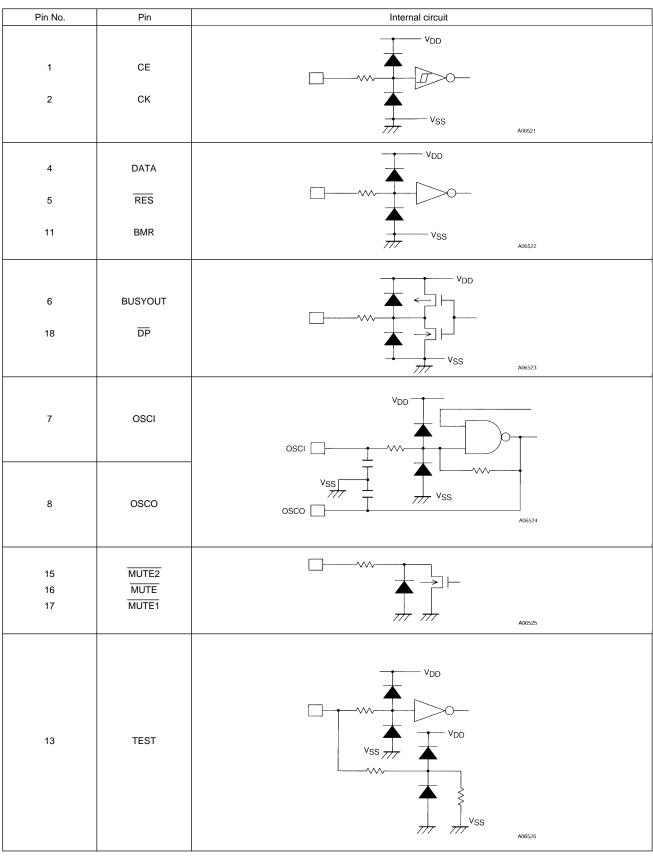

| 1       | CE              | I   | Set high when data is valid. This signal is also used when DTMF signals are issued consecutively in DTMF mode. The last DTMF signal is output until CE goes low. |

| 2       | СК              | I   | Data acquisition clock. Data is acquired on the rising edge of this signal.                                                                                      |

| 3       | NC              |     |                                                                                                                                                                  |

| 4       | DATA            | I   | Input for the 8-bit data.                                                                                                                                        |

| 5       | RES             | I   | Reset input. Apply a low level to this input to reset dialer operation when, for example, power is first applied.                                                |

| 6       | BUSYOUT         | 0   | Outputs a high level during dialer operation, including during pauses. This is a complementary output.                                                           |

| 7       | OSCI            | I   | Oscillator sizuit connections. Connect sitter a cructal or coronic 4 104204 MUIX socillator element to these nice                                                |

| 8       | OSCO            | 0   | Oscillator circuit connections. Connect either a crystal or ceramic 4.194304 MHz oscillator element to these pins.                                               |

| 9       | V <sub>SS</sub> |     | Power supply                                                                                                                                                     |

| 10      | V <sub>DD</sub> |     | rowei suppiy                                                                                                                                                     |

| 11      | BMR             | I   | Make ratio switching input. High: 33%, Low: 39%                                                                                                                  |

| 12      | NC              |     |                                                                                                                                                                  |

| 13      | TEST            | I   | LSI internal test pin. This pin either must be left open or must be tied low during normal operation.                                                            |

| 14      | DTMF            | 0   | DTMF output. This is an npn emitter-follower output.                                                                                                             |

| 15      | MUTE2           | 0   | DTMF mute output. This is an n-channel open-drain output.                                                                                                        |

| 16      | MUTE            | 0   | DP and DTMF mute output. This is an n-channel open-drain output.                                                                                                 |

| 17      | MUTE1           | 0   | DP mute output. This is an n-channel open-drain output.                                                                                                          |

| 18      | DP              | 0   | DP output. This can be either an n-channel open-drain output or a complementary output.                                                                          |

Unused inputs must always be tied to an appropriate logic level, i.e. either ground or  $V_{\mbox{\scriptsize DD}}.$

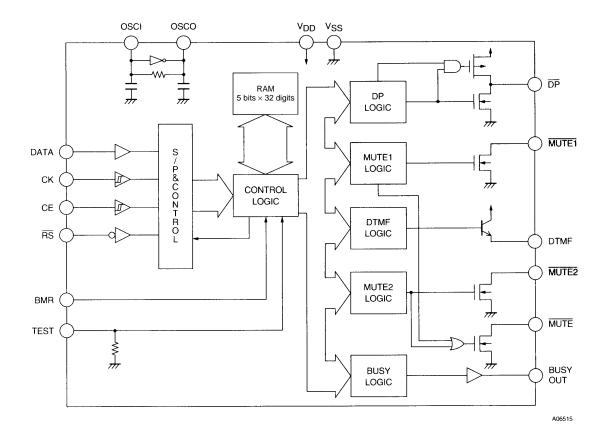

# **Block Diagram**

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | WRITE<br>TO RAM | Data interpretation and notes                                 |

|----|----|----|----|----|----|----|----|-----------------|---------------------------------------------------------------|

| Х  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | YES             | KEY D                                                         |

| Х  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | YES             | KEY 1                                                         |

| Х  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | YES             | KEY 2                                                         |

| Х  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | YES             | KEY 3                                                         |

| Х  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | YES             | KEY 4                                                         |

| Х  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | YES             | KEY 5                                                         |

| Х  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | YES             | KEY 6                                                         |

| Х  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | YES             | KEY 7                                                         |

| Х  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | YES             | KEY 8                                                         |

| Х  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | YES             | KEY 9                                                         |

| Х  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | YES             | KEY 0                                                         |

| Х  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | YES             | KEY *                                                         |

| Х  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | YES             | KEY #                                                         |

| Х  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | YES             | KEY A                                                         |

| Х  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | YES             | KEY B                                                         |

| Х  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | YES             | KEY C                                                         |

| Х  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | NO              | Illegal value                                                 |

| Х  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | NO              | Illegal value                                                 |

| Х  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | NO              | PAUSE clear (Only valid during a pause.)                      |

| Х  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | NO              | FLASH (707 or 277 ms)                                         |

| Х  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | NO              | STOP (Forced termination of a the current dialing operation.) |

| Х  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | NO              | RD (redial)                                                   |

| Х  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | NO              | MUTE ST                                                       |

| Х  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | NO              | MUTE END                                                      |

| Х  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | NO              | ON-HOOK                                                       |

| Х  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | NO              | OFF-HOOK                                                      |

| Х  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | YES             | MODE-CH (Pulse to tone single-direction change)               |

| Х  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | YES             | PAUSE (Pause for either 2.0 or 4.0 seconds.)                  |

#### Input Code Table

$\label{eq:constraint} \begin{array}{c} X: \text{Don't care} \\ \text{Only bits D0 to D4 are written to RAM.} \end{array}$

## Mode Settings Command Table

| D7 | D6   | D5   | D4          | D3        | D2           | D1        | D0         |

|----|------|------|-------------|-----------|--------------|-----------|------------|

| Х  | MODE | TEST | DPSEL       | PAUSE     | FLASH        | P/T       | DPR        |

| Х  | (1)  | (0)  | (0) N-CH OD | (0) 4.0 s | (0) 707.0 ms | (0) Tone  | (0) 20 pps |

| Х  | (1)  | (0)  | (0) CMP     | (1) 2.0 s | (1) 277.3 ms | (1) Pulse | (1) 10 pps |

Flash time Hooking pause time

707.0 ms......800.8 ms

277.3 ms.....1.23 s

Note that a hooking pause of 804.7 ms is also inserted automatically on a DP-off operation.

#### Mode Settings at Power On

When power is first applied, the initial settings listed in the table below are established according to the state of the BMR pin.

| BMR PIN   | DPSEL       | PAUSE     | FLASH        | P/T       | DPR        |

|-----------|-------------|-----------|--------------|-----------|------------|

| H (33.3%) | (0) N-CH OD | (0) 4.0 s | (0) 707.0 ms | (1) Pulse | (1) 10 pps |

| L (39.2%) | (0) N-CH OD | (0) 4.0 s | (0) 707.0 ms | (0) Tone  | (1) 10 pps |

# **Specifications**

# Absolute Maximum Ratings at Ta = $25^{\circ}$ C, $f_{OSC}$ = 4.194304 MHz

| Parameter                   | Symbol               | Conditions                             | Ratings                      | Unit |

|-----------------------------|----------------------|----------------------------------------|------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max  |                                        | -0.3 to +6.5                 | V    |

| Maximum input voltage       | V <sub>IN</sub> max  |                                        | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Maximum output voltage      | V <sub>OUT</sub> max |                                        | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Allowable power dissipation | Pd max               | Ta 70°C                                | 180                          | mW   |

| Minimum load resistance     | R <sub>L</sub> min   | Between the DTMF and the $V_{SS}$ pins | 1                            | k    |

| Operating temperature       | Topr                 |                                        | -30 to +70                   | °C   |

| Storage temperature         | Tstg                 |                                        | -40 to +125                  | °C   |

## Allowable Operating Ranges at $Ta = 25^{\circ}C$ , $f_{OSC} = 4.194304$ MHz

| Parameter                | Cumhal            | Conditions                      | Ratings             |     |                     | Unit |

|--------------------------|-------------------|---------------------------------|---------------------|-----|---------------------|------|

| Parameter                | Symbol Conditions |                                 | min                 | typ | max                 | Unit |

| Supply voltage           | V <sub>DDP</sub>  | Pulse mode                      | 1.5                 |     | 5.5                 | V    |

| Supply voltage           | V <sub>DDT</sub>  | DTMF mode                       | 2.0                 |     | 5.5                 | V    |

| Input high-level voltage | VIHS              | CK and CE input pins            | 0.8 V <sub>DD</sub> |     | $V_{DD}$            | V    |

|                          | VIH               | Input pins other than CK and CE | 0.7 V <sub>DD</sub> |     | $V_{DD}$            | V    |

| Input low-level voltage  | V <sub>ILS</sub>  | CK and CE input pins            | V <sub>SS</sub>     |     | 0.2 V <sub>DD</sub> | V    |

|                          | VIL               | Input pins other than CK and CE | V <sub>SS</sub>     |     | 0.3 V <sub>DD</sub> | V    |

| Oscillator pin rating    | f                 | Center frequency = 4.194304 MHz | -1.4                |     | +1.4                | %    |

|                          | R <sub>S</sub>    |                                 |                     |     | 100                 |      |

## Electrical Characteristics at Ta = $25^{\circ}$ C, f<sub>OSC</sub> = 4.194304 MHz

| Parameter                  | Symbol              | Conditions                                                                                                                                             |                      | Ratings |     | Unit |

|----------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|-----|------|

| Parameter                  | Symbol              | Conditions                                                                                                                                             | min                  | typ     | max | Unit |

|                            | I <sub>DDP</sub>    | In dial pulse output mode, output open $V_{DD}$ = 3.0 V : $V_{DD}$                                                                                     |                      | 0.3     | 0.5 | mA   |

| Quiescent current drain    | I <sub>DDT</sub>    | In DTMF output mode, output open,<br>$V_{DD} = 3.0 \text{ V}: V_{DD}$                                                                                  |                      | 0.5     | 1.0 | mA   |

|                            | I <sub>DD(ST)</sub> | Standby mode, output open $V_{DD} = 1.5$ to 5.5 V : $V_{DD}$                                                                                           |                      |         | 1   | μA   |

| Memory retention voltage   | V <sub>DR</sub>     | Between $V_{DD}$ and $V_{SS}$ : $V_{DD}$                                                                                                               | 1                    |         |     | V    |

| Memory retention current   | I <sub>DR</sub>     | $V_{DD} = 1.0 \text{ V} : V_{DD}$                                                                                                                      |                      |         | 0.5 | μA   |

|                            | I <sub>IHI</sub>    | $V_{IH} = V_{DD}, V_{DD} = 5.5 V : DATA, CK, CE, BMR, \overline{RS}$                                                                                   |                      |         | 1   | μA   |

| Input pin current          | I <sub>ILI</sub>    | $V_{IL} = V_{SS}, V_{DD} = 5.5 \text{ V}$ : DATA, CK, CE, BMR, $\overline{RS}$                                                                         | -1                   |         |     | μA   |

|                            | I <sub>IHIT</sub>   | $V_{IH} = V_{DD}, V_{DD} = 5.5 \text{ V}$ : TEST                                                                                                       |                      | 160     | 330 | μA   |

|                            | I <sub>ILIT</sub>   | $V_{IL} = V_{SS}, V_{DD} = 5.5 \text{ V}$ : TEST                                                                                                       | -1                   |         |     | μA   |

| Output pin leakage current | I <sub>OFF</sub>    | $V_{OH} = V_{DD}$ , $V_{DD} = 5.5$ V, when the output is off: BUSYOUT                                                                                  |                      |         | 1   | μA   |

|                            | V <sub>OH1</sub>    | V <sub>DD</sub> = 1.5 V, I <sub>OH</sub> = -250 μA : BUSYOUT                                                                                           | V <sub>DD</sub> –0.5 |         |     | V    |

|                            | V <sub>OH2</sub>    | $V_{DD} = 5.5 \text{ V}, I_{OH} = -1 \text{ mA} : \text{BUSYOUT}, \overline{\text{DP}},$<br>MUTE1, MUTE2, MUTE                                         | V <sub>DD</sub> –1   |         |     | V    |

| Output pin voltage         | V <sub>OL1</sub>    | $V_{DD}$ = 1.5 V, $I_{OL}$ = 250 µA : BUSYOUT, $\overline{DP}$ ,<br>MUTE1, MUTE2, MUTE                                                                 |                      |         | 0.4 | V    |

|                            | V <sub>OL2</sub>    | $\frac{V_{DD} = 5.5 \text{ V, } I_{OL} = 1 \text{ mA} : \text{BUSYOUT, } \overline{\text{DP}},}{\text{MUTE1, } \overline{\text{MUTE2, } \text{MUTE}}}$ |                      |         | 0.4 | V    |

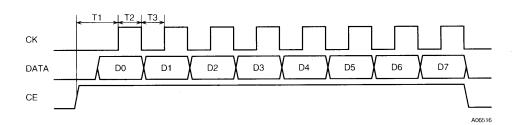

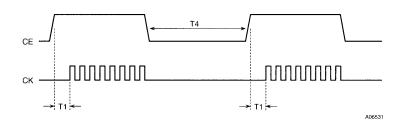

### **Dialer Input Format**

The serial data is input starting with the LSB.

T1 must be at least 6.5 µs (When an external clock is supplied to OSC1.)

If an oscillator element is used, T1 depends on the oscillator startup time for that oscillator element.

\*: For example, for ceramic oscillators, T1 will be about 1 ms ( $V_{DD} = 3.0$  to 5.5 V).

T2 and T3 must be at least  $1.0 \ \mu s$ .

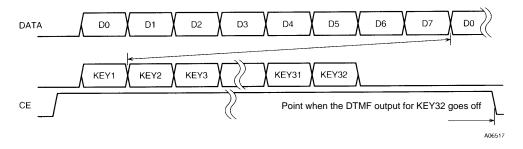

#### **Serial Data Sequential Input Format**

KEY1 to KEY31 are guaranteed by the DTMF output time.

\*: Continuous input is limited to dial data. Continuous input of mode setting commands is not possible.

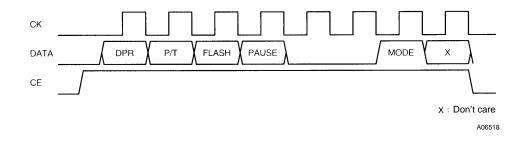

### **Mode Settings Format**

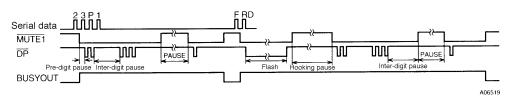

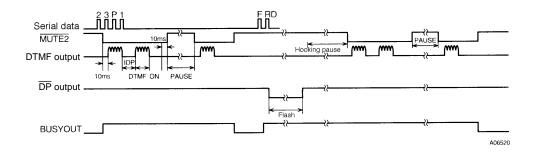

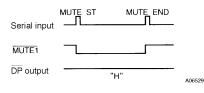

### **Timing Charts**

(1) Pulse mode

(2) Tone mode

## AC Characteristics at Ta = 25°C, $f_{OSC}$ = 4.194304 MHz

| Parameter                   | Symbol             | Conditions                                            |     | Ratings |     | Unit  |

|-----------------------------|--------------------|-------------------------------------------------------|-----|---------|-----|-------|

| Falameter                   | Symbol             |                                                       | min | typ     | max | Unit  |

|                             | -                  | When the D3 mode setting code is low (0)              |     | 4.0     |     | S     |

| Pause time                  | T <sub>AP</sub>    | When the D3 mode setting code is high (1)             |     | 2.0     |     | S     |

| DTMF output time            | T <sub>MFON</sub>  |                                                       |     | 100.6   |     | ms    |

|                             | -                  | For the first and later digits                        |     | 114.0   |     | ms    |

| DTMF inter-digit pause time | T <sub>MFOFF</sub> | For the last digit                                    |     | 109.9   |     | ms    |

|                             | -                  | When the D2 mode setting code is low (0)              |     | 707.0   |     | ms    |

| Flash time                  | T <sub>FL</sub>    | When the D2 mode setting code is high (1)             |     | 277.3   |     | ms    |

|                             | -                  | When the D2 mode setting code is low (0)              |     | 800.8   |     | ms    |

| Hooking pause time          | T <sub>HKP</sub>   | When the D2 mode setting code is high (1)             |     | 1.23    |     | s     |

| Low tone amplitude          | V <sub>OR</sub>    | V <sub>DD</sub> = 3.5 V, R <sub>L</sub> = 10 k        | 165 | 200     | 240 | mVrms |

| Tone output ratio           | dBCR               | $V_{DD}$ = 2.0 to 5.5 V, R <sub>L</sub> = 10 k        | 1   | 2       | 3   | dB    |

| Tone output distortion      | %DIS               | V <sub>DD</sub> = 2.0 to 5.5 V, R <sub>L</sub> = 10 k |     |         | 10  | %     |

## Pulse Output at Ta = $25^{\circ}$ C, f<sub>OSC</sub> = 4.194304 MHz

| DPR | BMR | Dial pulse rate | Pre-digit pause | Inter-digit pause | Make ratio |

|-----|-----|-----------------|-----------------|-------------------|------------|

| н   | н   | 9.97 PPS        | 33.3 + 10 ms    | 839.0 ms          | 33.3%      |

| н   | L   | 9.97 PPS        | 39.2 + 10 ms    | 844.9 ms          | 39.2%      |

| L   | н   | 19.93 PPS       | 16.7 + 10 ms    | 571.6 ms          | 33.3%      |

| L   | L   | 19.93 PPS       | 19.7 + 10 ms    | 574.6 ms          | 39.2%      |

## DTMF Output Frequencies at Ta = $25^{\circ}$ C, f<sub>OSC</sub> = 4.194304 MHz

|       | Output frequ | uency (Hz) |               |

|-------|--------------|------------|---------------|

| Input | Rating       | LC73701    | Deviation (%) |

| R1    | 697          | 697.2      | +0.027        |

| R2    | 770          | 769.9      | -0.016        |

| R3    | 852          | 851.8      | -0.023        |

| R4    | 941          | 941.3      | +0.029        |

| C1    | 1209         | 1209.4     | +0.036        |

| C2    | 1336         | 1335.8     | -0.018        |

| C3    | 1477         | 1476.9     | -0.009        |

| C4    | 1633         | 1633.3     | +0.018        |

### Internal Pin Circuits

Continued on next page.

#### Continued from preceding page.

#### Notes:

The LC73701M output ports are initialized to the following states when power is first applied. BUSYOUT and DP pins: Low

DTMF, MUTE1, MUTE, and MUTE2 pins: High-impedance

OSC0 pin: High

- (2) The following methods can be used to forcibly terminate dial output.

- 1. STOP command input

Output ports: The  $\overline{DP}$  and  $\overline{MUTE1}$  pins hold their previous states, all others are initialized.

Redialing is possible after a STOP command is input. However, this requires that a dialing operation had been performed previously.

2. Applying a low-level pulse (of at least 1  $\mu$ s) to the  $\overline{\text{RES}}$  pin. The operation is identical to that of the STOP command.

However, redialing is not possible after this hardware reset.

3. ON-HOOK command input

The  $\overline{\text{DP}}$  pin goes low, thus releasing the telephone line (circuit). Redialing is possible after an ON-HOOK command is input. However, if this dialing operation is performed, although DTMF signals will be output, since the  $\overline{\text{DP}}$  is low dial pulses will not be output. (Since the LSI performs a redial operation internally, the BUSYOUT pin will go high and the associated muting signal will also be output.)

4. OFF-HOOK command input

A hooking pause will be inserted automatically after the OFF-HOOK command input. Redialing is possible.

5. FLASH command input

A hooking pause will be inserted automatically after the FLASH command input. Redialing is possible.

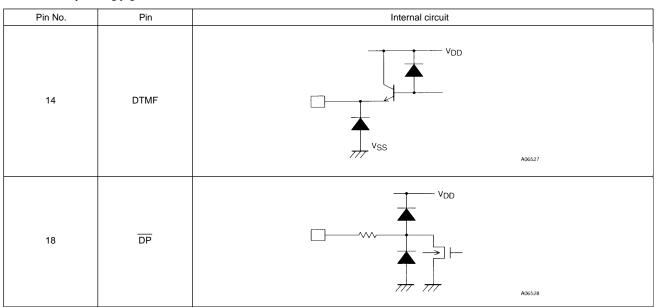

(3) The MUTE ST and MUTE END commands

These commands allows the  $\overline{\text{MUTE1}}$  pin to be controlled arbitrarily. The other muting outputs cannot be controlled explicitly.

The figure below shows the timing.

When a MUTE ST command is input, the MUTE1 pin goes low. During this low period, inputting pulse dial data will not cause the  $\overline{MUTE1}$  pin to return to the high level. That is, the low level is held until the next MUTE END command is input.

### (4) The ON-HOOK and OFF-HOOK commands

These commands allows the  $\overline{\text{DP}}$  pin to be controlled arbitrarily. The figure below shows the timing.

A hooking pause is inserted automatically when the OFF-HOOK command is input. The DP pin goes low when an ON-HOOK command is input. During this low period, inputting pulse dial data will not cause the DP pin to return to the high level. (Since the LSI performs a redial operation internally, the BUSYOUT pin will go high.) That is, the low level is held until the next OFF-HOOK command is input.

#### (5) The redial command

The redial operation re-outputs the dial data in the LC73701M's internal buffer memory. This buffer memory (redial memory) can hold up to 32 digits of dialing data. This means that if 33 or more digits of dialing data are input, earlier data will be overwritten starting with the thirty-third digit. After the following operations, the LC73701M will perform a redial operation if a redial command is input.

- 1. When a flash command is input after dialing data has been input

- 2. When an STOP command is input after dialing data has been input

- 3. When an ON-HOOK command is input after dialing data has been input

- 4. When an OFF-HOOK command is input after dialing data has been input

#### (6) Mode settings

The break/make ratio (BMR) is switched between 33% and 39% by the BMR pin. The BMR pin is initialized after power is first applied as shown in the table below.

| BMR PIN   | DPSEL       | PAUSE     | FLASH        | P/T       | DPR        |

|-----------|-------------|-----------|--------------|-----------|------------|

| H (33.3%) | (0) N-CH OD | (0) 4.0 s | (0) 707.0 ms | (1) Pulse | (1) 10 pps |

| L (39.2%) | (0) N-CH OD | (0) 4.0 s | (0) 707.0 ms | (0) Tone  | (1) 10 pps |

Settings other than BMR (i.e. DPR, P/T, FLASH, PAUSE, and DPSEL) are switched using mode commands. The information set by mode setting commands is stored internally by the LSI. Set the desired mode before inputting dial data. When dial data is written to the buffer memory, the P/T register data is attached to that dial data.

#### (7) Output pins during dialing and the redial operation

See the table below. The terms ON and OFF in the table below refer to the on or off state of the n-channel open drain output transistor.

|                  | DP                         | MUTE1                      | MUTE, MUTE2 | BUSYOUT | Redial memory      |

|------------------|----------------------------|----------------------------|-------------|---------|--------------------|

| Power on         | ON (L)                     | OFF                        | OFF         | L       | Readout is illegal |

| RES pin          | ON (L)                     | *1 OFF                     | OFF         | L       | Readout is illegal |

| STOP command     | *2 OFF (H)                 | *3 OFF                     | OFF         | L       | Readout allowed    |

| ON-HOOK command  | ON (L)                     | Retains the previous state | OFF         | L       | Readout allowed    |

| OFF-HOOK command | OFF (H)                    | Retains the previous state | OFF         | *4 H    | Readout allowed    |

| MUTE-ST command  | Retains the previous state | ON                         | OFF         | L       | Readout allowed    |

| MUTE-END command | Retains the previous state | OFF                        | OFF         | L       | Readout allowed    |

Notes: \*2 Turned off during dialing. However, since this command takes priority after an OFF-HOOK command is input, the on state is retained. \*1, 3: Turned off during dialing. However, since this command takes priority after a MUTE-ST command is input, the on state is retained.

\*4: Since a hooking pause is inserted automatically, this output goes high during that operation.

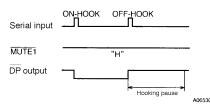

(8) CE input format (When an oscillator element is used.) The figure below shows the CE timing.

Although in the timing shown in the previous figure, T1 depends on the oscillator element startup time, here, this time does not need to be provided in the T1 period as long as it can be provided by the T4 period. For example, assume that the oscillator startup time when a ceramic oscillator is used is about 1 ms (when  $V_{DD} = 3.0$  to 5.5 V). In this case, this time must be provided by either setting T1 = 1 ms, or by setting T4 = 1 ms. However, note that T1 must be 6.5 µs or greater and T4 must be 1 µs or greater.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of May, 1997. Specifications and information herein are subject to change without notice.