LC8220

# JPEG Still Color Image Compression/Decompression LSI

# Preliminaly

### **Overview**

The LC8220 JPEG LSI implements digital still image compression and decompression conforming to the JPEG (Joint Photographic Expert Group) standard. The LC8220 includes the baseline system of the ISO 10918 (JPEG) standard, and requires no external components to construct an application that performs JPEG compliant compression/decompression.

# **Features**

- Conforms to the ISO 10918-1 baseline system

- Four quantization tables and four Huffman tables (two for AC and two for DC) are built in.

- · Hardware support for JPEG marker codes

- Built-in bidirectional YUV RGB converter

- Many color component sampling ratios are supported. (e.g., YUV 4:1:1 and YMCK 1:1:1:1, etc.)

- Level shift function that can be defined for each component

- · Built-in dual buffers for reduced data transfer load

- Bus sizing function that allows direct connection to 8-, 16-, and 32-bit busses

- Endian control function

- Three independent data buses

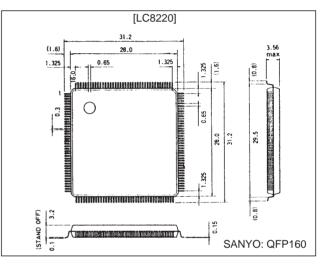

# **Package Dimensions**

unit: mm

### 3153A-QFP160

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

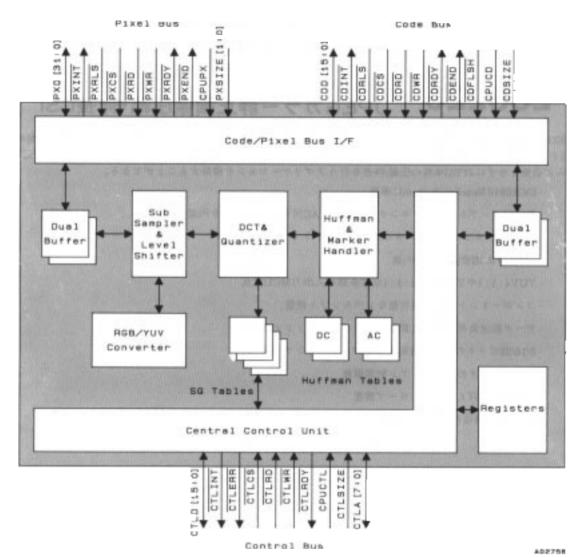

### **Block Diagram**

The LC8220 has three independent buses.

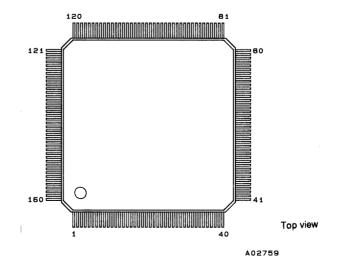

#### **Pin Assignment**

No. 4909-2/13

### **Pin Functions**

| Pin No. | Symbol                    | I/O      | Function                                                           |

|---------|---------------------------|----------|--------------------------------------------------------------------|

| 1       | V <sub>SS</sub>           |          | Ground                                                             |

| 2       | CTLCS                     | 1        | Control bus chip select*2                                          |

| 3       | CTLRD                     | 1        | Control bus read request <sup>*3</sup>                             |

| 4       | CTLWR                     |          | Control bus write request*4                                        |

| 5       | CTLRDY                    | 0        | Control bus ready for read/write requests*5                        |

| 6       | CTLERR                    | 0        | Error interrupt request                                            |

| 7       |                           | 0        | Control bus interrupt request                                      |

| 8       | CPUCTL                    | 1        | Connected CPU type setting for the control bus*1                   |

| 9       | CTLSIZE                   |          | Bus width selection for the control bus (0: 8 bits, 1: 16 bits)    |

| 10      | V <sub>DD</sub>           | <u> </u> | +5 V power supply                                                  |

| 10      | V <sub>SS</sub>           | <u> </u> | Ground                                                             |

| 12      | CTLA7                     | 1        |                                                                    |

| 12      | CTLA6                     | 1        |                                                                    |

| 13      | CTLA5                     |          |                                                                    |

| 14      | CTLA3                     |          |                                                                    |

| 15      | CTLA4<br>CTLA3            |          | Control address bus                                                |

| 16      | CTLA3<br>CTLA2            |          |                                                                    |

| 17      | CTLA2<br>CTLA1            |          |                                                                    |

| 18      | CTLAT                     |          |                                                                    |

|         |                           |          |                                                                    |

| 20      | V <sub>DD</sub>           |          | +5 V power supply                                                  |

| 21      | V <sub>SS</sub><br>CTLD15 | —        | Ground                                                             |

| 22      |                           | 1/0      |                                                                    |

| 23      | CTLD14                    | I/O      |                                                                    |

| 24      | CTLD13                    | I/O      |                                                                    |

| 25      | CTLD12                    | I/O      | Control data bus (D15 to D8 are unused if an 8-bit CPU is used.*7) |

| 26      | CTLD11                    | I/O      |                                                                    |

| 27      | CTLD10                    | I/O      |                                                                    |

| 28      | CTLD9                     | I/O      |                                                                    |

| 29      | CTLD8                     | I/O      |                                                                    |

| 30      | V <sub>DD</sub>           |          | +5 V power supply                                                  |

| 31      | V <sub>SS</sub>           | -        | Ground                                                             |

| 32      | CTLD7                     | I/O      |                                                                    |

| 33      | CTLD6                     | I/O      |                                                                    |

| 34      | CTLD5                     | I/O      |                                                                    |

| 35      | CTLD4                     | I/O      | Control data bus                                                   |

| 36      | CTLD3                     | I/O      |                                                                    |

| 37      | CTLD2                     | I/O      |                                                                    |

| 38      | CTLD1                     | I/O      |                                                                    |

| 39      | CTLD0                     | I/O      |                                                                    |

| 40      | V <sub>DD</sub>           | _        | +5 V power supply                                                  |

| 41      | V <sub>SS</sub>           |          | Ground                                                             |

| 42      | CLK                       |          | System clock                                                       |

| 43      | CLKSEL                    |          | Clock divisor selection (0: no divisor, 1: divisor used)*6         |

| 44      | RESET                     |          | System reset                                                       |

| 45      | TEST                      |          | Test mode selection (0: normal operation, 1: test mode)*6          |

| 46      | TESTOUT                   | 0        | Test result output*8                                               |

| 47      | MDD10                     | I/O      |                                                                    |

| 48      | MDD9                      | I/O      | Test mode data bus <sup>17</sup>                                   |

| 49      | MDD8                      | I/O      |                                                                    |

| 50      | V <sub>DD</sub>           |          | +5 V power supply                                                  |

| 51      | V <sub>SS</sub>           |          | Ground                                                             |

| 52      | MDD7                      | I/O      |                                                                    |

| 53      | MDD6                      | I/O      | Test mode data bus*7                                               |

| 54      | MDD5                      | I/O      |                                                                    |

Continued on next page.

Continued from preceding page.

| Pin No. | Symbol           | I/O | Function                                                                                            |

|---------|------------------|-----|-----------------------------------------------------------------------------------------------------|

| 55      | MDD4             | 1/0 |                                                                                                     |

| 56      | MDD3             | 1/0 | 1                                                                                                   |

| 57      | MDD2             | 1/0 | <br>Test mode data bus*7                                                                            |

| 58      | MDD1             | 1/0 |                                                                                                     |

| 59      | MDD0             | I/O | 1                                                                                                   |

| 60      | V <sub>DD</sub>  |     | +5 V power supply                                                                                   |

| 61      | V <sub>SS</sub>  | _   | Ground                                                                                              |

| 62      | TESTI1           | 1   |                                                                                                     |

| 63      | TESTI2           | 1   |                                                                                                     |

| 64      | TESTI2           | 1   | Test mode input pins <sup>*9</sup>                                                                  |

| 65      | TESTI4           |     |                                                                                                     |

| 66      | TESTI5           |     |                                                                                                     |

|         | TESTIS<br>TESTO1 | 0   |                                                                                                     |

| 67      | TESTO2           | 0   | Test mode output pins <sup>18</sup>                                                                 |

| 68      |                  |     | Test mede innut size                                                                                |

| 69      | TESTI6           |     | Test mode input pin <sup>eg</sup>                                                                   |

| 70      | TESTO3           | 0   | Test mode output pin <sup>18</sup>                                                                  |

| 71      |                  |     | Connected CPU type setting for the pixel bus*1                                                      |

| 72      | PXCS             |     | Pixel bus chip select*2                                                                             |

| 73      | PXRD             |     | Pixel bus read request*3                                                                            |

| 74      | PXWR             |     | Pixel bus write request*4                                                                           |

| 75      | PXRDY            | 0   | Pixel bus ready for read/write requests*5                                                           |

| 76      | PXINT            | 0   | Pixel bus interrupt request                                                                         |

| 77      | PXRLS            |     | Pixel bus interrupt release                                                                         |

| 78      | PXEND            | 0   | Pixel bus last data output indicator                                                                |

| 79      | (NC)             | _   |                                                                                                     |

| 80      | V <sub>DD</sub>  | _   | +5 V power supply                                                                                   |

| 81      | V <sub>SS</sub>  | _   | Ground                                                                                              |

| 82      | PXD31            | I/O |                                                                                                     |

| 83      | PXD30            | I/O |                                                                                                     |

| 84      | PXD29            | I/O |                                                                                                     |

| 85      | PXD28            | I/O | Pixel data bus                                                                                      |

| 86      | PXD27            | I/O | (D31 to D16 are unused if a 16-bit CPU is used and D31 to D8 are unused if an 8-bit CPU is used.*7) |

| 87      | PXD26            | I/O |                                                                                                     |

| 88      | PXD25            | I/O |                                                                                                     |

| 89      | PXD24            | I/O |                                                                                                     |

| 90      | V <sub>DD</sub>  | -   | +5 V power supply                                                                                   |

| 91      | V <sub>SS</sub>  | _   | Ground                                                                                              |

| 92      | PXD23            | I/O |                                                                                                     |

| 93      | PXD22            | I/O |                                                                                                     |

| 94      | PXD21            | I/O |                                                                                                     |

| 95      | PXD20            | I/O | Pixel data bus                                                                                      |

| 96      | PXD19            | I/O | (D31 to D16 are unused if a 16-bit CPU is used and D31 to D8 are unused if an 8-bit CPU is used.*7) |

| 97      | PXD18            | I/O |                                                                                                     |

| 98      | PXD17            | I/O |                                                                                                     |

| 99      | PXD16            | I/O |                                                                                                     |

| 100     | V <sub>DD</sub>  | _   | +5 V power supply                                                                                   |

| 101     | V <sub>SS</sub>  | _   | Ground                                                                                              |

| 102     | PXD15            | I/O |                                                                                                     |

| 103     | PXD14            | I/O |                                                                                                     |

| 104     | PXD13            | I/O |                                                                                                     |

| 105     | PXD12            | I/O | Pixel data bus                                                                                      |

| 106     | PXD11            | I/O | (D31 to D16 are unused if a 16-bit CPU is used and D31 to D8 are unused if an 8-bit CPU is used.*7) |

| 107     | PXD10            | I/O |                                                                                                     |

| 108     | PXD9             | I/O | 1                                                                                                   |

| 109     | PXD8             | I/O | 1                                                                                                   |

| ι       | 1                |     | Continued on next page                                                                              |

Continued on next page.

Continued from preceding page.

| I/O   | Function                                                        |

|-------|-----------------------------------------------------------------|

| —     | +5 V power supply                                               |

| _     | Ground                                                          |

| I/O   |                                                                 |

| I/O   | -                                                               |

| I/O   | -                                                               |

| I/O   | Pixel data bus                                                  |

| I/O   |                                                                 |

| I/O   | -                                                               |

| I/O   | -                                                               |

| I/O   | -                                                               |

|       | +5 V power supply                                               |

| _     | Ground                                                          |

| 1     | Bus width selection for the pixel bus                           |

| 1     | (PXSIZE [1,0] = 00: 8 bits, 01: 16 bits, 1*: 32 bits)           |

|       |                                                                 |

| 1     | Code bus chip select*2                                          |

|       | Code bus read request*3                                         |

|       | Code bus vrite request*4                                        |

| 0     | Code bus ready for read/write requests*5                        |

| 0     | Code bus interrupt request                                      |

| 1     | Code bus interrupt release                                      |

| 0     | Code bus last data output                                       |

|       |                                                                 |

| 1     | Code bus forcible buffer flush                                  |

|       | -                                                               |

|       | _                                                               |

|       | _                                                               |

|       | _                                                               |

|       |                                                                 |

| 1     | Connected CPU type setting for the code bus*1                   |

| 1     | Bus width setting for the code bus (0: 8 bits, 1: 16 bits)      |

|       | +5 V power supply                                               |

| _     | Ground                                                          |

| I/O   |                                                                 |

| I/O   |                                                                 |

| I/O   |                                                                 |

| I/O   | Code data bus (D15 to D8 are unused if an 8-bit CPU is used.*7) |

| I/O   |                                                                 |

| I/O   |                                                                 |

| I/O   |                                                                 |

| I/O   |                                                                 |

| —     | +5 V power supply                                               |

| —     | Ground                                                          |

| I/O   |                                                                 |

| I/O   |                                                                 |

| I/O   |                                                                 |

| I/O   | Code data bue                                                   |

| I/O   | - Code data bus                                                 |

| I/O   | 1                                                               |

| I/O   | 1                                                               |

| I/O   | 1                                                               |

| _     | +5 V power supply                                               |

| ems a | I/O                                                             |

Note 1, 2, 3, 4, 5: These items are related to the CPU type. ound).

| 6: | Connect to | V <sub>SS</sub> | (gro |

|----|------------|-----------------|------|

|    |            |                 |      |

Must be pulled up. These are NC pins. Connect to V<sub>DD</sub>. 0: 7: 8: 9:

|                            | Z**CS <sup>2</sup> | Z**RD3 | Z**WR4 | Z**RDY5 |

|----------------------------|--------------------|--------|--------|---------|

| 8086 family CPU (CPU = 1)  | CS                 | RD     | WR     | RDY     |

| 68000 family CPU (CPU = 0) | AS                 | R/W    | DS     | ACK     |

# **Specifications**

# Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , GND = 0 V

| Parameter              | Symbol                          | Conditions                   | Ratings                       | Unit |

|------------------------|---------------------------------|------------------------------|-------------------------------|------|

| Maximum supply voltage | V <sub>DD</sub> max             |                              | -0.3 to +7.0                  | V    |

| I/O voltages           | V <sub>I</sub> , V <sub>O</sub> |                              | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Operating temperature  | Topr                            |                              | -30 to +70                    | °C   |

| Storage temperature    | Tstg                            |                              | -55 to +125                   | °C   |

| Soldoring tomporature  |                                 | Hand soldering: 3 seconds    | 350                           | °C   |

| Soldering temperature  |                                 | Reflow soldering: 10 seconds | 235                           | °C   |

### Allowable Operating Ranges at Ta = -30 to $+70^{\circ}C$ , GND = 0 V

| Parameter      | Symbol          | Conditions | min | typ | max             | Unit |

|----------------|-----------------|------------|-----|-----|-----------------|------|

| Supply voltage | V <sub>DD</sub> |            | 4.5 |     | 5.5             | V    |

| Input voltage  | V <sub>IN</sub> |            | 0   |     | V <sub>DD</sub> | V    |

## DC Characteristics at Ta = -30 to +70°C, $V_{DD}$ = 4.5 to 5.5 V, GND = 0 V

| Parameter                 | Symbol          | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | min                   | typ | max   | Unit |

|---------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-------|------|

| Input high level voltage  | VIH             | TTL compatible: CTLCS, CTLRD, CTLWR, CPUCTL,<br>CTLSIZE, CTLA7 to CTLA0, CLKSEL, RESET, TEST,<br>CTLD15 to CTLD0                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.2                   |     |       | V    |

| Input low level voltage   | VIL             | TTL compatible: CPUPX, PXCS, PXRD, PXWR,<br>PXD31 to PXD0, PXRLS, PXSIZE0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |     | 0.8   | V    |

| Input leakage current     | IL.             | PXSIZE1, CDCS, CDRD, CDWR, CDRLS, CDFLSH,<br>CPUCD, CDSIZE, CDD15 to CDD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -10                   |     | +10   | μΑ   |

| Output high level voltage | V <sub>OH</sub> | $\label{eq:comparameters} \begin{array}{l} I_{OH} = -3 \text{ mA, TTL compatible: } \overline{\text{CTLRDY}}, \overline{\text{CTLERR}}, \\ \overline{\text{CTLINT}}, \overline{\text{TESTOUT}}, \overline{\text{CTLD15}} \text{ to } \overline{\text{CTLD0}}, \overline{\text{PXRDY}}, \\ \overline{\text{PXINT}}, \overline{\text{PXEND}}, \overline{\text{PXD31}} \text{ to } \overline{\text{PXD0}}, \overline{\text{CDRDY}}, \overline{\text{CDINT}}, \\ \overline{\text{CDEND}}, \overline{\text{CDD15}} \text{ to } \overline{\text{CDD0}} \end{array}$ | V <sub>DD</sub> – 2.1 |     |       | V    |

| Output low level voltage  | V <sub>OL</sub> | $\label{eq:comparameters} \begin{array}{l} I_{OH} = -3 \\ \hline CTLINT, \ TESTOUT, \ CTLD15 \ to \ CTLD0, \ \overrightarrow{PXRDY}, \\ \hline PXINT, \ \overrightarrow{PXEND}, \ PXD31 \ to \ PXD0, \ \overrightarrow{CDRDY}, \ \overrightarrow{CDINT}, \\ \hline \overrightarrow{CDEND}, \ CDD15 \ to \ CDD0 \end{array}$                                                                                                                                                                                                                                   |                       |     | 0.4   | V    |

| Output leakage current    | I <sub>OZ</sub> | For high impedance outputs: CTLD15 to CTLD0,<br>PXD31 to PXD0, CDD15 to CDD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -10                   |     | +10   | μA   |

| Oscillator frequency      | fosc            | CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                       |     | 16.67 | MHz  |

| Current drain             | I <sub>DD</sub> | V <sub>DD</sub> = 5.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       | 145 |       | mA   |

#### **AC Characteristics**

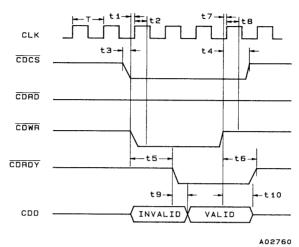

Code Bus Interface Timing

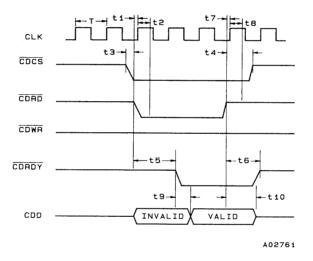

Code Bus Read Cycle

Code Bus Read Cycle (type 1)

|     | Item                                                             | Minimum | Maximum     | Unit |

|-----|------------------------------------------------------------------|---------|-------------|------|

| t1  | Read signal assert setup time (referenced to CLK)                | 8       |             | ns   |

| t2  | Read signal assert hold time (referenced to CLK)                 | 15      |             | ns   |

| t3  | Chip select stabilization time (referenced to the read signal)   | 0       |             | ns   |

| t4  | Chip select hold time (referenced to the read signal)            | 0       |             | ns   |

| t5  | Ready signal response delay time (referenced to the read signal) |         | T + t1 + 20 | ns   |

| t6  | Ready signal release delay time (referenced to the read signal)  |         | t7 + 27     | ns   |

| t7  | Read signal negate setup time (referenced to CLK)                | 8       |             | ns   |

| t8  | Read signal negate hold time (referenced to CLK)                 | 15      |             | ns   |

| t9  | Data output delay time (referenced to the ready signal)          |         | 15          | ns   |

| t10 | Data output hold time (referenced to the read signal)            |         | t7 + 15     | ns   |

| Т   | Clock period                                                     | 60      |             | ns   |

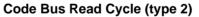

Code Bus Write Cycle

Code Bus Write Cycle (type 1)

|     | Item                                                                             | Minimum | Maximum     | Unit |

|-----|----------------------------------------------------------------------------------|---------|-------------|------|

| t1  | Write signal assert setup time (referenced to CLK)                               | 8       |             | ns   |

| t2  | Write signal assert hold time (referenced to CLK)                                | 15      |             | ns   |

| t3  | Chip select stabilization time (referenced to the write signal)                  | 0       |             | ns   |

| t4  | Chip select hold time (referenced to the write signal)                           | 0       |             | ns   |

| t5  | Write cycle selection signal stabilization time (referenced to the write signal) | 0       |             | ns   |

| t6  | Write cycle selection signal hold time (referenced to the write signal)          | 0       |             | ns   |

| t7  | Ready signal response delay time (referenced to the write signal)                |         | T + t1 + 20 | ns   |

| t8  | Ready signal release delay time (referenced to the write signal)                 |         | t9 + 27     | ns   |

| t9  | Write signal negate setup time (referenced to CLK)                               | 8       |             | ns   |

| t10 | Write signal negate hold time (referenced to CLK)                                | 15      |             | ns   |

| t11 | Data setup time (referenced to the ready signal)                                 | 45      |             | ns   |

| t12 | Data hold time (referenced to the ready signal)                                  | 15      |             | ns   |

| Т   | Clock period                                                                     | 60      |             | ns   |

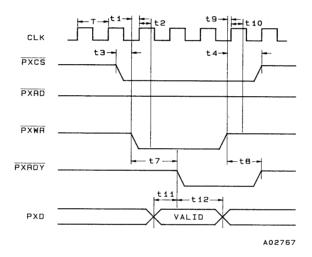

Pixel Bus Interface Timing

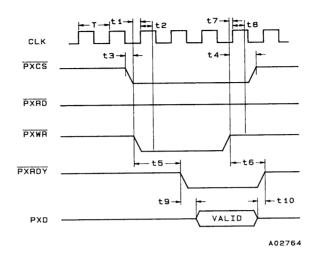

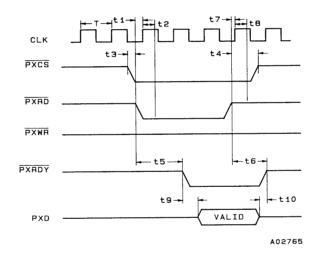

Pixel Bus Read Cycle

Pixel Bus Read Cycle (type 1)

|     | Item                                                             | Minimum | Maximum     | Unit |

|-----|------------------------------------------------------------------|---------|-------------|------|

| t1  | Read signal assert setup time (referenced to CLK)                | 8       |             | ns   |

| t2  | Read signal assert hold time (referenced to CLK)                 | 15      |             | ns   |

| t3  | Chip select stabilization time (referenced to the read signal)   | 5       |             | ns   |

| t4  | Chip select hold time (referenced to the read signal)            | 5       |             | ns   |

| t5  | Ready signal response delay time (referenced to the read signal) |         | T + t1 + 20 | ns   |

| t6  | Ready signal release delay time (referenced to the read signal)  |         | t7 + 28     | ns   |

| t7  | Read signal negate setup time (referenced to CLK)                | 8       |             | ns   |

| t8  | Read signal negate hold time (referenced to CLK)                 | 15      |             | ns   |

| t9  | Data output delay time (referenced to the ready signal)          |         | 15          | ns   |

| t10 | Data output hold time (referenced to the read signal)            |         | t7 + 18     | ns   |

| Т   | Clock period                                                     | 60      |             | ns   |

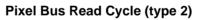

Pixel Bus Write Cycle

Pixel Bus Write Cycle (type 1)

|     | Item                                                                             | Minimum | Maximum     | Unit |

|-----|----------------------------------------------------------------------------------|---------|-------------|------|

| t1  | Write signal assert setup time (referenced to CLK)                               | 8       |             | ns   |

| t2  | Write signal assert hold time (referenced to CLK)                                | 15      |             | ns   |

| t3  | Chip select stabilization time (referenced to the write signal)                  | 5       |             | ns   |

| t4  | Chip select hold time (referenced to the write signal)                           | 5       |             | ns   |

| t5  | Write cycle selection signal stabilization time (referenced to the write signal) | 5       |             | ns   |

| t6  | Write cycle selection signal hold time (referenced to the write signal)          | 5       |             | ns   |

| t7  | Ready signal response delay time (referenced to the write signal)                |         | T + t1 + 20 | ns   |

| t8  | Ready signal release delay time (referenced to the write signal)                 |         | t9 + 28     | ns   |

| t9  | Write signal negate setup time (referenced to CLK)                               | 8       |             | ns   |

| t10 | Write signal negate hold time (referenced to CLK)                                | 15      |             | ns   |

| t11 | Data setup time (referenced to the ready signal)                                 | 60      |             | ns   |

| t12 | Data hold time (referenced to the ready signal)                                  | 20      |             | ns   |

| Т   | Clock period                                                                     | 60      |             | ns   |

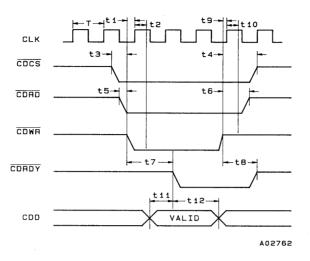

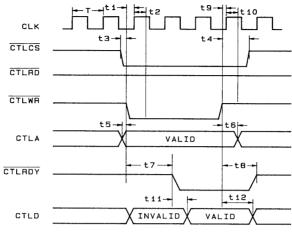

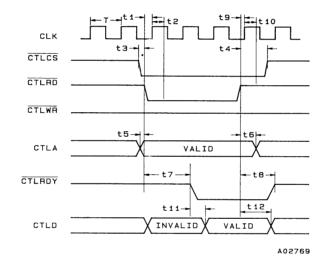

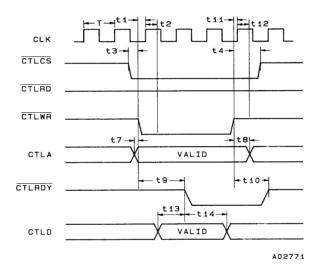

Control Bus Interface Timing

#### Control Bus Read Cycle

A02768

### Control Bus Register Read Cycle (type 1)

### Control Bus Register Read Cycle (type 2)

|     | Item                                                             | Minimum | Maximum     | Unit |

|-----|------------------------------------------------------------------|---------|-------------|------|

| t1  | Read signal assert setup time (referenced to CLK)                | 10      |             | ns   |

| t2  | Read signal assert hold time (referenced to CLK)                 | 15      |             | ns   |

| t3  | Chip select stabilization time (referenced to the read signal)   | 10      |             | ns   |

| t4  | Chip select hold time (referenced to the read signal)            | 15      |             | ns   |

| t5  | Address stabilization time (referenced to the read signal)       | 0       |             | ns   |

| t6  | Address hold time (referenced to the read signal)                | 5       |             | ns   |

| t7  | Ready signal response delay time (referenced to the read signal) |         | T + t1 + 24 | ns   |

| t8  | Ready signal release delay time (referenced to the read signal)  |         | t9 + 30     | ns   |

| t9  | Read signal negate setup time (referenced to CLK)                | 12      |             | ns   |

| t10 | Read signal negate hold time (referenced to CLK)                 | 15      |             | ns   |

| t11 | Data output delay time (referenced to the ready signal)          |         | 0           | ns   |

| t12 | Data output hold time (referenced to the read signal)            |         | t9 + 30     | ns   |

| Т   | Clock period                                                     | 60      |             | ns   |

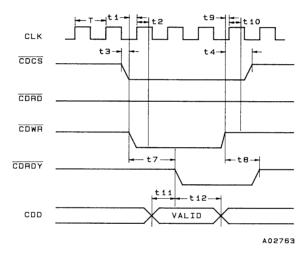

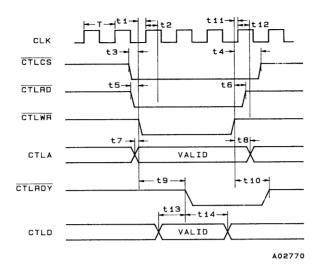

Control Bus Write Cycle

## Control Bus Register Write Cycle (type 1)

Control Bus Register Write Cycle (type 2)

|     | Item                                                                             | Minimum | Maximum     | Unit |

|-----|----------------------------------------------------------------------------------|---------|-------------|------|

| t1  | Write signal assert setup time (referenced to CLK)                               | 12      |             | ns   |

| t2  | Write signal assert hold time (referenced to CLK)                                | 15      |             | ns   |

| t3  | Chip select stabilization time (referenced to the write signal)                  | 10      |             | ns   |

| t4  | Chip select hold time (referenced to the write signal)                           | 15      |             | ns   |

| t5  | Write cycle selection signal stabilization time (referenced to the write signal) | 10      |             | ns   |

| t6  | Write cycle selection signal hold time (referenced to the write signal)          | 10      |             | ns   |

| t7  | Address stabilization time (referenced to the write signal)                      | 0       |             | ns   |

| t8  | Address hold time (referenced to the write signal)                               | 5       |             | ns   |

| t9  | Ready signal response delay time (referenced to the write signal)                |         | T + t1 + 24 | ns   |

| t10 | Ready signal release delay time (referenced to the write signal)                 |         | t11 + 32    | ns   |

| t11 | Write signal negate setup time (referenced to CLK)                               | 5       |             | ns   |

| t12 | Write signal negate hold time (referenced to CLK)                                | 15      |             | ns   |

| t13 | Data setup time (referenced to the ready signal)                                 | 60      |             | ns   |

| t14 | Data hold time (referenced to the ready signal)                                  | 20      |             | ns   |

| Т   | Clock period                                                                     | 60      |             | ns   |

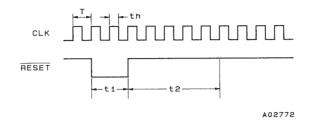

Hardware Reset Timing

#### Hardware Reset Timing

|    | ltem                     | Minimum | Maximum | Unit |

|----|--------------------------|---------|---------|------|

| t1 | Reset signal pulse width | 2T      |         | ns   |

| t2 | LSI access disabled time | 5T      |         | ns   |

| Т  | Clock period             | 60      |         | ns   |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1997. Specifications and information herein are subject to change without notice.