# **CD-ROM Decoder with Built-in SCSI Interface**

# **Preliminary**

#### Overview

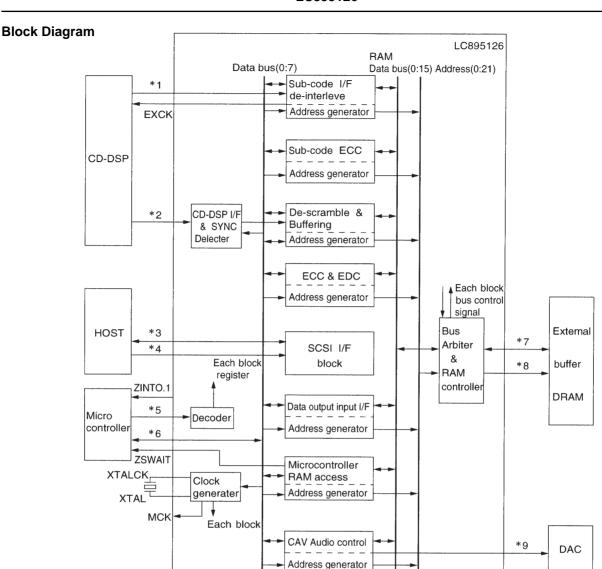

The LC895126 is a CD-ROM decoder that in addition to CD-ROM functions also provides a built-in SCSI interface.

# **Functions**

CD-ROM ECC functions, subcode read function, SCSI interface, CAV audio functions

# **Features**

- Built-in SCSI interface (Includes a SCAM selection register)

- Supports 24× playback and a 10MB/sec data transfer rate (when 16-bit data path 70-ns EDO DRAM is used).

- Supports the use of up to 4 Mbit of buffer RAM.

- Users can freely set up the CD main channel, C2 flag, and other areas in buffer RAM.

- Batch transfer function (Function that transfers the CD main channel, C2 flag, and other data in a single operation)

- Multiblock transfer function (Function that transfers multiple blocks automatically in a single operation)

- Subcode ECC functions and CD-Text support

- CAV audio functions

- Intelligent functions (Including auto buffering, auto decoding, and CD-R support)

Supports 20MB/s transfers (This capability is currently under evaluation (July 1997) and cannot be guaranteed at present.)

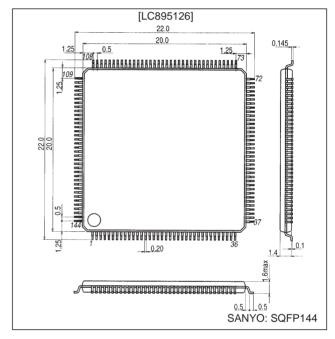

# **Package Dimensions**

unit: mm

#### 3214-SQFP144

#### **Specifications**

#### Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , $V_{SS} = 0$ V

| Parameter                        | Symbol                          | Conditions | Ratings                      | Unit |

|----------------------------------|---------------------------------|------------|------------------------------|------|

| Maximum supply voltage           | V <sub>DD</sub> max             |            | -0.3 to +7.0                 | V    |

| Input and output voltage         | V <sub>I</sub> , V <sub>O</sub> |            | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Allowable power dissipation      | Pd max                          | Ta ≤ 70°C  | 550                          | mW   |

| Operating temperature            | Topr                            |            | -30 to +70                   | °C   |

| Storage temperature              | Tstg                            |            | -55 to +125                  | °C   |

| Soldering conditions (pins only) |                                 | 10 seconds | 260                          | °C   |

#### Allowable Operating Ranges at $Ta = -30 \text{ to } +70^{\circ}\text{C}$ , $V_{SS} = 0 \text{ V}$

| Parameter           | Symbol          | Conditions |     | Unit |          |       |

|---------------------|-----------------|------------|-----|------|----------|-------|

| Faianielei          | Symbol          | Conditions | min | typ  | max      | Offic |

| Supply voltage      | V <sub>DD</sub> |            | 4.5 | 5.0  | 5.5      | V     |

| Input voltage range | V <sub>IN</sub> |            | 0   |      | $V_{DD}$ | V     |

#### Electrical Characteristics at Ta = -30 to +70°C, $V_{SS} = 0$ V, $V_{DD} = 4.5$ to 5.5 V

| Dozomotor                 | Cumbal            | Conditions                                   | Ratings               |     |                     | Unit  |  |

|---------------------------|-------------------|----------------------------------------------|-----------------------|-----|---------------------|-------|--|

| Parameter                 | Symbol            | Symbol Conditions                            |                       | typ | max                 | Oille |  |

| Input high-level voltage  | V <sub>IH</sub> 1 | TTI level since (4)                          | 2.2                   |     |                     | V     |  |

| Input low-level voltage   | V <sub>IL</sub> 1 | - TTL level pins: (1)                        |                       |     | 0.8                 | V     |  |

| Input high-level voltage  | V <sub>IH</sub> 2 | TTL level pins: (9)                          | 2.2                   |     |                     | V     |  |

| Input low-level voltage   | V <sub>IL</sub> 2 | Pins with built-in pull-up resistors.        |                       |     | 0.8                 | V     |  |

| Input high-level voltage  | V <sub>IH</sub> 3 | TTL level pins: (2)                          | 2.2                   |     |                     | V     |  |

| Input low-level voltage   | V <sub>IL</sub> 3 | Schmitt input pins                           |                       |     | 0.8                 | V     |  |

| Input high-level voltage  | V <sub>IH</sub> 4 | CMOS level pins: (3)                         | 0.8 V <sub>DD</sub>   |     |                     | V     |  |

| Input low-level voltage   | V <sub>IL</sub> 4 | Schmitt input pins                           |                       |     | 0.2 V <sub>DD</sub> | V     |  |

| Input high-level voltage  | V <sub>IH</sub> 5 | (4), (8), (10)                               | 2.0                   |     |                     | V     |  |

| Input low-level voltage   | V <sub>IL</sub> 5 |                                              |                       |     | 0.8                 | V     |  |

| Output high-level voltage | V <sub>OH</sub> 1 | I <sub>OH</sub> 1 = -12 mA : (6)             | V <sub>DD</sub> – 2.1 |     |                     | V     |  |

| Output low-level voltage  | V <sub>OL</sub> 1 | I <sub>OL</sub> 1 = 12 mA : (6)              |                       |     | 0.4                 | V     |  |

| Output high-level voltage | V <sub>OH</sub> 2 | $I_{OH}2 = -8 \text{ mA} : (7)$              | 2.4                   |     |                     | V     |  |

| Output low-level voltage  | V <sub>OL</sub> 2 | I <sub>OL</sub> 2 = 8 mA : (7)               |                       |     | 0.4                 | V     |  |

| Output high-level voltage | V <sub>OH</sub> 2 | $I_{OH}2 = -2 \text{ mA} : (9), (5)$         | 2.4                   |     |                     | V     |  |

| Output low-level voltage  | V <sub>OL</sub> 2 | I <sub>OL</sub> 2 = 2 mA : (9), (5)          |                       |     | 0.4                 | V     |  |

| Output low-level voltage  | V <sub>OL</sub> 4 | I <sub>OL</sub> 4 = 48 mA : (10)             |                       |     | 0.4                 | V     |  |

| Input leakage current     | I <sub>IL</sub>   | $V_I = V_{SS}$ or $V_{DD}$ : All input pins. | -25                   |     | +25                 | μA    |  |

| Pull-up resistance        | R <sub>UP</sub>   | (5), (9)                                     | 60                    | 120 | 240                 | kΩ    |  |

The pin sets referred to above are as follows:

INPÚT

TEST0 to TEST4, CSCTRL, SUA0 to SUA6, X1EN, WFCK, SBS0 C2PO, SDATA, BCK, LRCK, SCOR, ZRESET ZCS, ZRD, ZWR SCSISEL, XTALSEL

(3) (4)

OUTPUT

(5) ZINTO, ZINT1, ZSWAIT

(6)

MCK, MCK2, MCK3

EXCK, DSDATA, DLRCK, DBCK, ZRAS0, ZRAS1, ZCAS0, ZCAS1, ZOE, ZUWE, ZLWE, RA0 to RA8

INOUT

(8) ACK, ATN (9) D0 to D7, IO0 to IO15, IOP0 to IOP4 (10) DB0 to DB7, DBP, BSY, I/O, MSG, SEL, RST, REQ, C/D

Note: The XTAL0, XTALCK0, XTAL1, and XTALCK1 pins are not covered by the electrical characteristics.

# **SCSI Interface Pin Input Characteristics**

| Parameter               | Symbol              | Conditions                       | Ratings |      |      | Unit |

|-------------------------|---------------------|----------------------------------|---------|------|------|------|

| Farameter               |                     | Conditions                       | min     | typ  | max  | Onit |

| Input threshold voltage | V <sub>t + t1</sub> | V <sub>DD</sub> = 4.50 to 5.50 V |         | 1.60 | 2.00 | V    |

| Input theshold voltage  | $V_{t-t1}$          |                                  | 0.80    | 1.10 |      | V    |

| Hysteresis              | ΔV <sub>tt1</sub>   | V <sub>DD</sub> = 5.0 V          | 0.41    | 0.5  |      | V    |

#### **Active Negation Output Characteristics**

| Parameter                 | Symbol          | Conditions               |     | Unit |     |       |

|---------------------------|-----------------|--------------------------|-----|------|-----|-------|

| Farameter                 | Symbol          | Conditions               | min | typ  | max | Offic |

| Output high-level voltage | V <sub>OH</sub> | I <sub>OH</sub> = -24 mA | 2.5 |      |     | V     |

| Output low-level voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 48 mA  |     |      | 0.4 | V     |

Note: Active negation refers to the  $\overline{DB0}$  to  $\overline{DB7}$ ,  $\overline{REQ}$ , and  $\overline{DBPB}$  outputs.

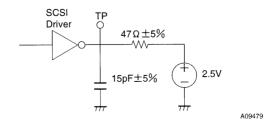

Figure 1

# **Pin Functions**

I: Input pin, O: Output pin, B: Bidirectional pin, P: Power Supply pin, NC: Not Connection pin

| Pin No. | Symbol           | Туре     | Function                                                                                                                                      |

|---------|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>SS0</sub> | Р        |                                                                                                                                               |

| 2       | IO2              | В        | Duffers DAM date 1/0 mins                                                                                                                     |

| 3       | IO1              | В        | Buffer RAM data I/O pins.                                                                                                                     |

| 4       | 100              | В        | Built in pull-up resistors.                                                                                                                   |

| 5       | MCK2SEL          | 1        | Provided for switching between MCK2 (22 MHz, 20 MHz) and MCK3 (27 MHz, 25 MHz) in PLL mode. Currently, must be connected to V <sub>DD</sub> . |

| 6       |                  | NC       |                                                                                                                                               |

| 7       | V <sub>SS0</sub> | Р        |                                                                                                                                               |

| 8       | V <sub>SS0</sub> | Р        |                                                                                                                                               |

| 9       | V <sub>SS0</sub> | Р        |                                                                                                                                               |

| 10      |                  | NC       |                                                                                                                                               |

| 11      |                  | NC       |                                                                                                                                               |

| 12      | C2PO             | 1        |                                                                                                                                               |

| 13      | SDATA            | ı        | CD DOD interfere                                                                                                                              |

| 14      | BCK              | ı        | CD DSP interface                                                                                                                              |

| 15      | LRCK             | 1        |                                                                                                                                               |

| 16      | EXCK             | 0        |                                                                                                                                               |

| 17      | WFCK             | 1        | Subcode I/O                                                                                                                                   |

| 18      | V <sub>DD</sub>  | Р        |                                                                                                                                               |

| 19      | V <sub>SS0</sub> | Р        |                                                                                                                                               |

| 20      | SBSO             | 1        |                                                                                                                                               |

| 21      | SCOR             | ı        | Subcode I/O                                                                                                                                   |

| 22      | DSDATA           | 0        |                                                                                                                                               |

| 23      | DLRCK            | 0        | D/A converter outputs                                                                                                                         |

| 24      | DBCK             | 0        |                                                                                                                                               |

| 25      | MCK              | 0        | Outputs the XTALCK1 state (1/1, 1/2, or stopped)                                                                                              |

| 26      | V <sub>SS0</sub> | Р        |                                                                                                                                               |

| 27      | XTALCK0          | ı        | Crystal oscillator circuit input                                                                                                              |

| 28      | XTAL0            | 0        | Crystal oscillator circuit input                                                                                                              |

| 29      | TEST0            | ı        |                                                                                                                                               |

| 30      | TEST1            | ı        |                                                                                                                                               |

| 31      | TEST2            | ı        | Test pins. These pins must be connected to V <sub>SS0</sub> .                                                                                 |

| 32      | TEST3            | ı        |                                                                                                                                               |

| 33      | TEST4            | ı        |                                                                                                                                               |

| 34      | MCK2             | 0        |                                                                                                                                               |

| 35      | MCK3             | 0        | Outputs the XTALCK0 state (1/1, 1/2, 1/512, or stopped)                                                                                       |

| 36      | V <sub>SS0</sub> | Р        |                                                                                                                                               |

| 37      | V <sub>DD</sub>  | Р        |                                                                                                                                               |

| 38      | ZRESET           | 1        | Chip reset. The system is reset by a low-level input.                                                                                         |

| 39      | ZRD              | 1        | Microcontroller data read signal input                                                                                                        |

| 40      | ZWR              | l i      | Microcontroller data write signal input                                                                                                       |

|         |                  | <u> </u> |                                                                                                                                               |

Continued on next page.

# Continued from preceding page.

| Pin No. | Symbol           | Туре | Function                                                                                                                                          |

|---------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 41      | ZCS              | I    | Register chip select signal input from the microcontroller                                                                                        |

| 42      | CSCTRL           | ı    | CS active low/active high selection input from the microcontroller                                                                                |

| 43      | SUA0             | ı    |                                                                                                                                                   |

| 44      | SUA1             | ı    |                                                                                                                                                   |

| 45      | SUA2             | ı    |                                                                                                                                                   |

| 46      | SUA3             | ı    | Microcontroller register selection signals                                                                                                        |

| 47      | SUA4             | ı    |                                                                                                                                                   |

| 48      | SUA5             | ı    |                                                                                                                                                   |

| 49      | SUA6             | ı    |                                                                                                                                                   |

| 50      | D0               | В    |                                                                                                                                                   |

| 51      | D1               | В    |                                                                                                                                                   |

| 52      | D2               | В    | Microcontroller data signals                                                                                                                      |

| 53      | D3               | В    |                                                                                                                                                   |

| 54      | V <sub>DD</sub>  | Р    |                                                                                                                                                   |

| 55      | V <sub>SS0</sub> | Р    |                                                                                                                                                   |

| 56      | D4               | В    |                                                                                                                                                   |

| 57      | D5               | В    |                                                                                                                                                   |

| 58      | D6               | В    |                                                                                                                                                   |

| 59      | D7               | В    |                                                                                                                                                   |

| 60      | ZINT0            | 0    | Interrupt request signal output to the microcontroller (ECC side. Set up by register settings.)                                                   |

| 61      | ZINT1            | 0    | Interrupt request signal output to the microcontroller (SCSI side. Set up by register settings.)                                                  |

| 62      | ZSWAIT           | 0    | Wait signal output to the microcontroller                                                                                                         |

| 63      | V <sub>SS0</sub> | Р    |                                                                                                                                                   |

| 64      | IOP0             | В    |                                                                                                                                                   |

| 65      | IOP1             | В    |                                                                                                                                                   |

| 66      | IOP2             | В    | General-purpose I/O                                                                                                                               |

| 67      | IOP3             | В    |                                                                                                                                                   |

| 68      | IOP4             | В    |                                                                                                                                                   |

| 69      | X1EN             | ı    | Must be tied low in versions without a PLL circuit. Must be connected to V <sub>DD</sub> through a resistor in versions that use the PLL circuit. |

| 70      | ZTALCK1          | ı    | Shock proof function oscillator circuit input. Used by the PLL circuit in PLL versions.                                                           |

| 71      | XTAL1            | 0    | Shock proof function oscillator circuit output. Used by the PLL circuit in PLL versions.                                                          |

| 72      | V <sub>SS0</sub> | Р    | Analog system ground in PLL versions                                                                                                              |

| 73      | V <sub>DD</sub>  | Р    | Analog system power supply in PLL versions                                                                                                        |

| 74      | V <sub>SS1</sub> | Р    |                                                                                                                                                   |

| 75      | I/O              | В    |                                                                                                                                                   |

| 76      | REQ              | В    | SCSI interface connections                                                                                                                        |

| 77      | V <sub>SS1</sub> | Р    |                                                                                                                                                   |

| 78      | C/D              | В    | SCCI interfere connections                                                                                                                        |

| 79      | SEL              | В    | SCSI interface connections                                                                                                                        |

| 80      |                  | NC   |                                                                                                                                                   |

| 81      | V <sub>DD</sub>  | Р    |                                                                                                                                                   |

| 82      | V <sub>SS1</sub> | Р    |                                                                                                                                                   |

| 83      | MSG              | В    | SCCI interface connections                                                                                                                        |

| 84      | RST              | В    | SCSI interface connections                                                                                                                        |

| 85      | V <sub>SS1</sub> | Р    |                                                                                                                                                   |

| 86      | ACK              | В    | SCCI interface connections                                                                                                                        |

| 87      | BSY              | В    | SCSI interface connections                                                                                                                        |

| 88      | V <sub>SS1</sub> | Р    |                                                                                                                                                   |

Continued on next page.

# Continued from preceding page.

| Pin No. | Symbol           | Туре | Function                                                 |

|---------|------------------|------|----------------------------------------------------------|

| 89      | ATN              | В    | SCSI interface connections                               |

| 90      | $V_{DD}$         | Р    |                                                          |

| 91      | V <sub>SS1</sub> | Р    |                                                          |

| 92      |                  | NC   |                                                          |

| 93      | DBP              | В    | SCSI interface connections                               |

| 94      | V <sub>DD</sub>  | Р    |                                                          |

| 95      | DB7              | В    | COOL interference and anti-                              |

| 96      | DB6              | В    | SCSI interface connections                               |

| 97      | V <sub>SS1</sub> | Р    |                                                          |

| 98      | DB5              | В    | COOL interference and anti-                              |

| 99      | DB4              | В    | SCSI interface connections                               |

| 100     | V <sub>DD</sub>  | Р    |                                                          |

| 101     | DB3              | В    | SCSI interface connections                               |

| 102     | DB2              | В    | SCSI IIILEHACE CONTECTIONS                               |

| 103     | V <sub>SS1</sub> | Р    |                                                          |

| 104     | DB1              | В    | SCSI interface connections                               |

| 105     | DB0              | В    | SOST INTERIACE CONTROLLORS                               |

| 106     | SCSISEL          | I    | SCSI pin assignment selection (No change when held low.) |

| 107     | XTALSEL          | I    | XATL oscillator selection in PLL mode                    |

| 108     | V <sub>SS1</sub> | Р    |                                                          |

| 109     | V <sub>DD</sub>  | Р    |                                                          |

| 110     | V <sub>SS0</sub> | Р    |                                                          |

| 111     | ZRAS0            | 0    | RAS output 0 for buffer RAM (Normally, RAS 0 is used.)   |

| 112     | ZRAS1            | 0    | RAS output 1 for buffer RAM                              |

| 113     | ZCAS0            | 0    | CAS output 0 for buffer RAM (Normally, CAS 0 is used.)   |

| 114     | ZCAS1            | 0    | CAS output 1 for buffer RAM                              |

| 115     | ZOE              | 0    | Buffer RAM output enable                                 |

| 116     | ZUWE             | 0    | Buffer RAM upper write enable                            |

| 117     | ZLWE             | 0    | Buffer RAM lower write enable                            |

| 118     | V <sub>SS0</sub> | Р    |                                                          |

| 119     | RA0              | 0    |                                                          |

| 120     | RA1              | 0    |                                                          |

| 121     | RA2              | 0    |                                                          |

| 122     | RA3              | 0    | Buffer RAM address outputs                               |

| 123     | RA4              | 0    |                                                          |

| 124     | RA5              | 0    |                                                          |

| 125     | RA6              | 0    |                                                          |

| 126     | V <sub>DD</sub>  | Р    |                                                          |

| 127     | V <sub>SS0</sub> | Р    |                                                          |

| 128     | RA7              | 0    | Buffer RAM address outputs                               |

| 129     | RA8              | 0    | · ·                                                      |

| 130     | RA9 (IO15)       | В    | Buffer RAM address and data outputs.                     |

| 131     | RA10 (IO14)      | В    | Built in pull-up resistors.                              |

Continued on next page.

#### Continued from preceding page.

| Pin No. | Symbol           | Туре | Function                     |

|---------|------------------|------|------------------------------|

| 132     | IO13             | В    |                              |

| 133     | IO12             | В    |                              |

| 134     | IO11             | В    | Buffer RAM data I/O.         |

| 135     | IO10             | В    | Built in pull-up resistors.  |

| 136     | 109              | В    |                              |

| 137     | IO8              | В    |                              |

| 138     | V <sub>SS0</sub> | Р    |                              |

| 139     | 107              | В    |                              |

| 140     | IO6              | В    | Buffer RAM data I/O.         |

| 141     | IO5              | В    | Built in pull-up resistors.  |

| 142     | 104              | В    | Duilt iii puil-up resistors. |

| 143     | IO3              | В    |                              |

| 144     | $V_{DD}$         | Р    |                              |

NC pins must be left open.

Pin names that start with a 'Z' are negative logic (i.e. active low) pins.

V<sub>SS0</sub> is the logic system ground, and V<sub>SS1</sub> is the SCSI interface system ground.

If DRAM is used, undershoot prevention measures, such as inserting resistors in the RAS and CAS lines and inserting capacitors to ground, must be taken. Since this IC includes buffers that sink 48 mA, applications must take adequate noise reduction measures.

- \*1 WFCK. SBSO. SCOR

- \*2 BCK, SDATA, LRCK, C2PO

- \*3 DB0 to DB7, DBP, BSY, MSG, SEL, RST, REQ, I/O, C/D

- \*4 ACK, ATN

- \*5 ZRD, ZWR, SUA0 to AUA6, ZCS, CSCTRL

- \*6 D0 to D7

- \*7 IO0 to IO15

- \*8 RA0 to RA10, ZRAS0, ZRAS1, ZCAS0, ZCAS1, ZOE, ZUWE, ZLWE

- \*9 DBCK, DLRCK, DSDATA

Note: The pins IO15 and RA9 share pin 130, and the pins IO14 and RA10 share pin 131.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- 2 Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of January, 1998. Specifications and information herein are subject to change without notice.

A09480