# LE25CB643TT-BH

# **CMOSIC** 64 kb SPI CMOS Serial EEPROM

The LE25CB643TT-BH (hereinafter referred to as 'this device') is serial peripheral interface EEPROM (Electrically Erasable and Programmable ROM). This device realizes high speed and a high level reliability by incorporating high performance CMOS EEPROM technology. This device is compatible with SPI memory protocol, therefore it is best suited for application that requires re-writable nonvolatile parameter memory. And this device has 32bytes page write function for high speed data re-write.

# Function

- Capacity

- Single supply voltage

- Operating temperature

- Interface

- Operating clock frequency

- Low Power consumption

- : Standby

- : Read

- : Write

- Write cycle time

- Erase/Write cycles

- Data Retention

- High reliability

: 2.7V to 5.5V : -40°C to +85°C : SPI Mode0 and Mode3 correspondence

: 64k bits  $(8k \times 8 \text{ bits})$

- : 5MHz

- : 3µA (max.)

- : 1mA (max.)

- : 3mA (max.)

- Automatic page write mode : 32 Bytes : 5ms

- - $: 10^6$  cycles

- : 20 years

- : Adopts proprietary symmetric memory array configuration (USP6947325)

- Incorporates a feature to prohibit write operations under low voltage conditions.

- Package

- : LE25CB643TT-BH Micro8

\* This product is licensed from Silicon Storage Technology, Inc. (USA).

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 17 of this data sheet.

Micro8

## **Specifications**

## **Absolute Maximum Ratings** at $Ta = 25^{\circ}C$

| Parameter           | Symbol | Conditions | Ratings      | Unit |

|---------------------|--------|------------|--------------|------|

| Supply voltage      |        |            | -0.5 to +6.5 | V    |

| DC input voltage    |        |            | -0.5 to 5.5  | V    |

| Over-shoot voltage  |        |            | -1.0 to 6.5  | V    |

| Storage temperature | Tstg   |            | -65 to +150  | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **Recommended Operating Conditions**

| Parameter                | Conditions | Conditions | Ratings |     |     | Unit |

|--------------------------|------------|------------|---------|-----|-----|------|

| Parameter                | Symbol     | Conditions | min     | typ | max | Unit |

| Operating supply voltage |            |            | 2.7     |     | 5.5 | V    |

| Operating temperature    |            |            | -40     |     | +85 | °C   |

#### **DC Electrical Characteristics**

| Parameter                       | Symbol            | Conditions                                                                                                                  |                    | Ratings |                      | Unit |  |

|---------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------|---------|----------------------|------|--|

| Parameter                       | Symbol            | conditions mir                                                                                                              |                    | typ     | max                  | Unit |  |

| Power supply current at reading | ICCR              | $\overline{\text{CS}} = 0.1 \text{V}_{\text{DD}}, \overline{\text{HOLD}} = \overline{\text{WP}} = 0.9 \text{V}_{\text{DD}}$ |                    |         | 1                    | mA   |  |

|                                 |                   | $SI = 0.1V_{DD}/0.9V_{DD}$ , SO =open                                                                                       |                    |         |                      |      |  |

|                                 |                   | clock frequency = 5MHz, $V_{DD} = V_{DD}$ max                                                                               |                    |         |                      |      |  |

| Power supply current at writing | ICCW              | $V_{DD} = V_{DD} \max$ , $V_{IN} = 0.1 V_{DD} / 0.9 V_{DD}$                                                                 |                    |         | 3                    | mA   |  |

| CMOS standby current            | I <sub>SB</sub>   | $\overline{CS} = V_{DD}, V_{IN} = V_{DD} \text{ or } V_{SS}$                                                                |                    |         | 3                    | μA   |  |

|                                 |                   | V <sub>DD</sub> = V <sub>DD</sub> max                                                                                       |                    |         |                      |      |  |

| Input leakage current           | ILI               | $V_{IN} = V_{SS}$ to $V_{DD}$ , $V_{DD} = V_{DD}$ max                                                                       |                    |         | 2                    | μΑ   |  |

| Output leakage current          | ILO               | $V_{IN} = V_{SS}$ to $V_{DD}$ , $V_{DD} = V_{DD}$ max                                                                       |                    |         | 2                    | μA   |  |

| Input low voltage               | VIL               | V <sub>DD</sub> = V <sub>DD</sub> max                                                                                       | -0.3               |         | 0.3V <sub>DD</sub>   | V    |  |

| Input high voltage              | VIH               | $V_{DD} = V_{DD} \min$                                                                                                      | 0.7V <sub>DD</sub> |         | V <sub>DD</sub> +0.3 | V    |  |

| Output low voltage              | V <sub>OL</sub>   | $I_{OL}$ = 3.0mA, $V_{DD}$ = 2.7V to 5.5V                                                                                   |                    |         | 0.4                  | V    |  |

| Output high voltage             | V <sub>OH</sub> 1 | $I_{OH}$ = 0.4mA, $V_{DD}$ = 2.7V to 5.5V                                                                                   | 0.8V <sub>DD</sub> |         |                      | V    |  |

#### **Capacitance** at $Ta = 25^{\circ}C$ , f = 1MHz

| Parameter                 | Symbol          | Conditions           | Ratings | Unit |

|---------------------------|-----------------|----------------------|---------|------|

| In/Output pin capacitance | C <sub>DQ</sub> | $V_{DQ} = 0V$        | 12      | pF   |

| Input pin capacitance     | C <sub>IN</sub> | V <sub>IN</sub> = 0V | 6       | pF   |

Note: This parameter is sampled and not 100% tested.

#### **AC Electric Characteristics**

| Input pulse level            | $0.2 \times V_{DD}$ to $0.8 \times V_{DD}$ |

|------------------------------|--------------------------------------------|

| Input pulse rise / fall time | 10ns                                       |

| Output detection voltage     | $0.5 \times V_{DD}$                        |

| Output load                  | 30pF                                       |

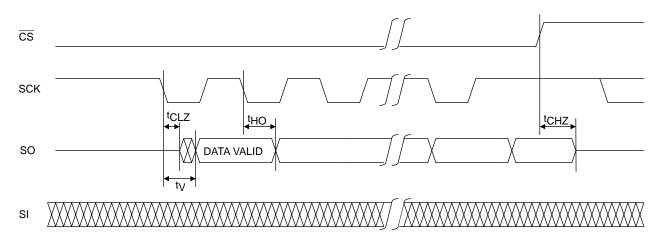

# AC characteristic (f<sub>CLK</sub> = 5MHz Operation) $V_{DD}$ = 2.7V to 5.5V

| Parameter                  | Cumbal            | Rati | ngs | Unit |  |

|----------------------------|-------------------|------|-----|------|--|

| Parameter                  | Symbol            | min  | max | Onit |  |

| Clock frequency            | <sup>f</sup> CLK  |      | 5   | MHz  |  |

| SCK High pulse width       | <sup>t</sup> CLHI | 90   |     | ns   |  |

| SCK Low pulse width        | <sup>t</sup> CLLO | 90   |     | ns   |  |

| Input rising, falling time | <sup>t</sup> RF   |      | 1   | μs   |  |

| CS Setup time              | tCSS              | 90   |     | ns   |  |

| SCK Setup time             | <sup>t</sup> CLS  | 90   |     | ns   |  |

| Data Setup time            | tDS               | 20   |     | ns   |  |

| Data Hold time             | <sup>t</sup> DH   | 30   |     | ns   |  |

| CS Hold time               | <sup>t</sup> CSH  | 90   |     | ns   |  |

| SCK Hold time              | <sup>t</sup> CLH  | 90   |     | ns   |  |

| CS Standby pulse width     | <sup>t</sup> CPH  | 90   |     | ns   |  |

| CS to High-Z output        | <sup>t</sup> CHZ  |      | 150 | ns   |  |

| SCK to output valid        | tv                |      | 80  | ns   |  |

| Output data hold time      | <sup>t</sup> HO   | 0    |     | ns   |  |

| WP Setup time              | tWPS              | 30   |     | ns   |  |

| WP Hold time               | twph              | 30   |     | ns   |  |

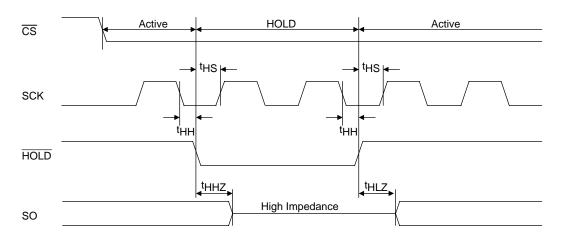

| HOLD Setup time            | tHS               | 30   |     | ns   |  |

| HOLD Hold time             | tнн               | 30   |     | ns   |  |

| HOLD High to Low-Z Output  | tHLZ              |      | 50  | ns   |  |

| HOLD Low to High-Z Output  | <sup>t</sup> HHZ  |      | 100 | ns   |  |

| Write cycle time           | tWC               |      | 5   | ms   |  |

| SCK to Low-Z output        | <sup>t</sup> CLZ  | 0    |     | ns   |  |

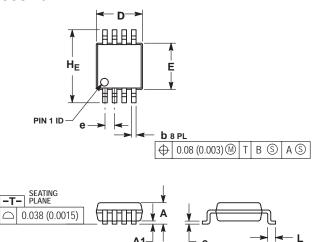

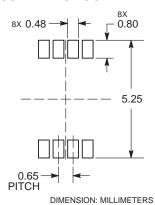

## **Package Dimensions**

unit : mm

#### Micro8<sup>™</sup>

CASE 846A-02 **ISSUE J**

RECOMMENDED **SOLDERING FOOTPRINT\***

c

A1

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

NOTES:

1. 2.

- LS: DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER. DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE. 3.

- DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE. 846A-01 OBSOLETE, NEW STANDARD 846A-02. 4. 5.

|     | MILLIMETERS |      |      |       | INCHES    |       |

|-----|-------------|------|------|-------|-----------|-------|

| DIM | MIN         | NOM  | MAX  | MIN   | NOM       | MAX   |

| Α   |             |      | 1.10 |       |           | 0.043 |

| A1  | 0.05        | 0.08 | 0.15 | 0.002 | 0.003     | 0.006 |

| b   | 0.25        | 0.33 | 0.40 | 0.010 | 0.013     | 0.016 |

| с   | 0.13        | 0.18 | 0.23 | 0.005 | 0.007     | 0.009 |

| D   | 2.90        | 3.00 | 3.10 | 0.114 | 0.118     | 0.122 |

| E   | 2.90        | 3.00 | 3.10 | 0.114 | 0.118     | 0.122 |

| е   | 0.65 BSC    |      |      |       | 0.026 BSC | ;     |

| L   | 0.40        | 0.55 | 0.70 | 0.016 | 0.021     | 0.028 |

| HE  | 4.75        | 4.90 | 5.05 | 0.187 | 0.193     | 0.199 |

#### GENERIC **MARKING DIAGRAM\***

XXXX = Specific Device Code А

- = Assembly Location

- Y = Year

- W = Work Week

- = Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " •", may or may not be present.

| STYLE 1:                 | STYLE 2:                   | STYLE 3:                   |

|--------------------------|----------------------------|----------------------------|

| PIN 1. SOURCE            | PIN 1. SOURCE 1            | PIN 1. N-SOURCE            |

| 2. SOURCE                | 2. GATE 1                  | 2. N-GATE                  |

| <ol><li>SOURCE</li></ol> | <ol><li>SOURCE 2</li></ol> | <ol><li>P-SOURCE</li></ol> |

| 4. GATE                  | 4. GATE 2                  | 4. P-GATE                  |

| 5. DRAIN                 | 5. DRAIN 2                 | 5. P-DRAIN                 |

| 6. DRAIN                 | 6. DRAIN 2                 | 6. P-DRAIN                 |

| 7. DRAIN                 | 7. DRAIN 1                 | 7. N-DRAIN                 |

| 8. DRAIN                 | 8. DRAIN 1                 | 8. N-DRAIN                 |

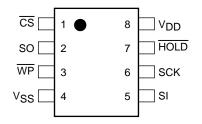

# **Pin Assignment**

# **Pin Descriptions**

| PIN1 | CS              | Chip select        |

|------|-----------------|--------------------|

| PIN2 | SO              | Serial data output |

| PIN3 | WP              | Write-protect      |

| PIN4 | VSS             | Ground             |

| PIN5 | SI              | Serial data input  |

| PIN6 | SCK             | Serial clock       |

| PIN7 | HOLD            | Hold               |

| PIN8 | V <sub>DD</sub> | Power supply       |

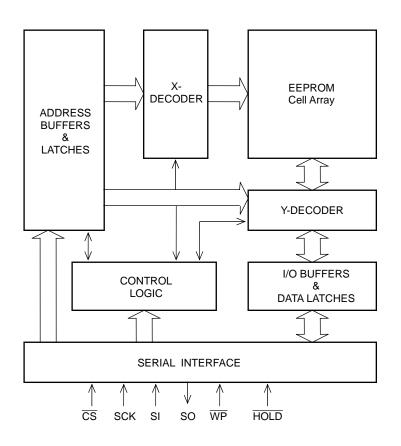

# **Block Diagram**

| Command                         | The 1st bus cycle | The 2nd bus cycle | The 3rd bus cycle | The 4th bus cycle | The 5th bus cycle | The 6th bus<br>cycle | The n-th bus cycle |

|---------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|--------------------|

| Write enable<br>(WREN)          | 06h               |                   |                   |                   |                   |                      |                    |

| Write disable<br>(WRDI)         | 04h               |                   |                   |                   |                   |                      |                    |

| Status Register Read<br>(RDSR)  | 05h               |                   |                   |                   |                   |                      |                    |

| Status Register Write<br>(WRSR) | 01h               | DATA              |                   |                   |                   |                      |                    |

| Read                            | 03h               | A15-A8            | A7-A0             |                   |                   |                      |                    |

| Write                           | 02h               | A15-A8            | A7-A0             | PD *1             | PD *1             | PD *1                | PD *1              |

Definition of Table 1 :

h = hexadecimal notation, A15 to A13 are don't care for all commands.

\*1. PD: page write data. The arbitrary numbers of data of 1 to 32 bytes of byte unit for input.

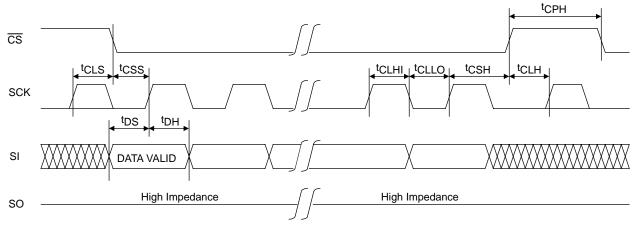

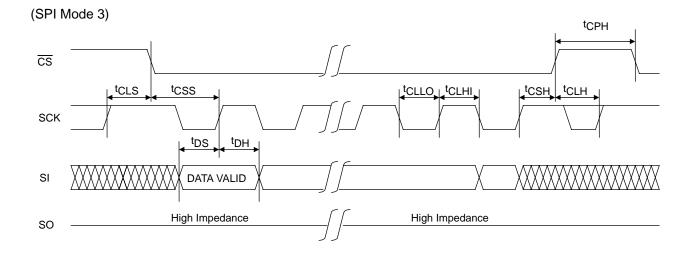

#### Figure 2: Serial Input Timing Diagram

(SPI Mode 0)

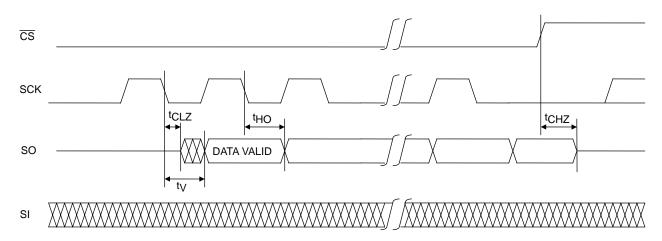

# Figure 3: Serial Output Timing Diagram

(SPI Mode 0)

(SPI Mode 3)

## **Command definition**

Table1 contains a command list and a brief summary of the commands. The following is a detailed description of the options initiated by each command.

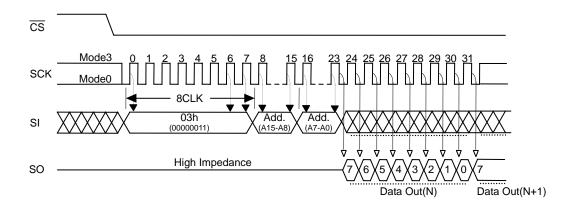

#### 1. Read (Read)

The read operation is constituted from the 1st bus cycle to the 4th bus cycle. If 16-bit address is inputted after OP-code (03h), the data of the specified address will be outputted synchronizing with SCK. A data is outputted from the falling edge clock of the 4th bus cycle Bit0. Figure4 shows timing waveform of a Read operation.

While having inputted SCK, the increment of the address is automatically carried out inside a device, and data is outputted in order until the top address up to. If the data is outputted and the input of SCK continues still more, it returns to the lowest address (0000h) and a data output is continued.

By making  $\overline{CS}$  into a logic high level, a device is deselecting, and read cycle is ended. Output terminal will be in a high impedance state.

#### Figure 4: Read Timing Diagram

- A15 to A13: Don't Care

- SI inputs the command and Address synchronizing with rising edge of 0 to 23rd SCK clock.

- SO outputs the data synchronizing with falling edge of SCK of after 23rd SCK clock.

#### 2. Status Register

The Status Register can perform detection state of a device and setup of protection. The register consists of 8 bits. The Status Register's contents are shown in Table2.

| Bit  | Name     | Logic                     | Function                               | Default at Power up      |

|------|----------|---------------------------|----------------------------------------|--------------------------|

| Dito | Bit0 RDY |                           | Ready state                            |                          |

| BILU |          |                           | Busy state (Write operation progress)  | 0                        |

| Ditt |          | 0 Write prohibition state |                                        | <u>_</u>                 |

| Bit1 | WEN      | 1                         | Write possible state                   | 0                        |

| Bit2 | вро 0    |                           |                                        | Non-volatile information |

| BILZ |          | 1                         | The block protect information          |                          |

| Bit3 |          | 0                         | Reference Status Registers BP0 and BP1 | Non-volatile Information |

| Bilo | BP1      | 1                         |                                        | Non-volatile information |

| Bit4 | Х        | 0                         | Reserve Bit                            | 0                        |

| Bit5 | Х        | 0                         | Reserve Bit                            | 0                        |

| Bit6 | Х        | 0                         | Reserve Bit                            | 0                        |

| 0.47 |          | 0                         | Status Register Write enable state     |                          |

| Bit7 | SRWP     | 1                         | Status Register Write disable state    | Non-volatile Information |

#### Table 2 : Status Register

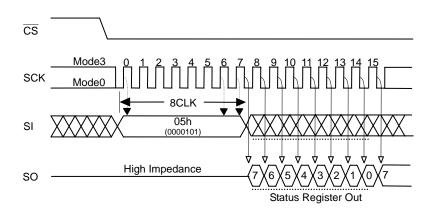

#### 2-1. Status Register Read (RDSR)

Status Register Read can read the Status Register's contents, moreover it can read also during the write operation. Figure 5 shows timing waveform of a Status Register Read.

Status Register command consists of only the 1st bus, If OP-code (05h) dose writes in, synchronizing with falling edge of SCK, the Status Register's contents will be outputted from SRWP (Bit7).

If the data is outputted until RDY (Bit0), and also SCK input continues still more, it returns to SRWP and data output is continued. Data is outputted from the falling edge clock of the 1st bus cycle Bit0.

Status Register Read can be read always (also in case of inside of write cycle).

Figure 5: Read Status Register Timing Diagram

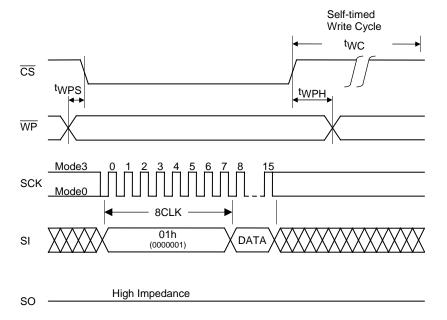

#### 2-2. Status Register Write (WRSR)

By Status Register Write, BP0, BP1 and SRWP can be rewritten. RDY, WEN, Bit4, Bit5 and Bit6 are read-only, BP0, BP1 and SRWP are non-volatile.

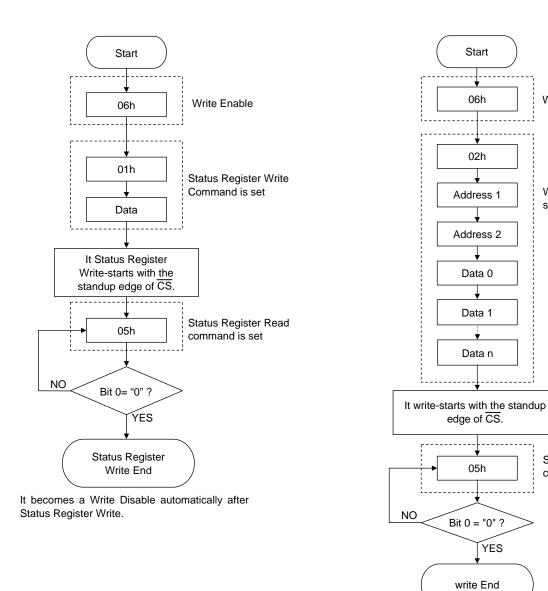

A timing waveform is shown in Figure6 and a flow chart is shown in Figure11.

Status Register Write command consists of the 1st bus cycle and the 2nd bus cycle, and internal Write operation starts with the rising edge of  $\overline{CS}$  after inputting data after OP-code (01h). Internal write operation is automatically performed inside the device and a Status Register Write rewrites BP0, BP1 and SRWP non-volatilized data. The write-in data to read-only bits ( $\overline{RDY}$ , WEN, Bit4, Bit5, Bit 6) are don't care.

The end of a Status Register Write is detectable with  $\overline{\text{RDY}}$  of a Status Register Read.

The number of times of rewriting of a Status Register Write is 1,000 times (Min).

In order to perform a Status Register Write, it is necessary to change WEN of a Status Register into "1" state for  $\overline{WP}$  pin.

#### Figure 6: Status Register Write Timing Diagram

#### 2-3. Status Register Description

#### RDY (Bit0)

The end of a Write is detectable with  $\overline{\text{RDY}}$ . If device is in a busy state  $\overline{\text{RDY}}$  is in "1", and the Write will be ended in "0" states.

#### WEN (Bit1)

It is detectable whether a Write is possible with WEN. If WEN is in "0" state, even if it inputs a Write command, Device will not perform write operation. If WEN is in "1" state, Write is possible to the area by which block protection is not carried out.

WEN is controllable with a Write Enable command and a Write disable command. WEN will be in "1" state with a Write Enable command (06h), and will be in "0" states with a Write disable command (04h).

Moreover, in the following state, automatically, WEN will be in "0" states and an unprepared Write will be prevented.

- At the time of a power-up

- After a write is completed

- After a Status Register Write is completed

\* WEN keeps previous status, if input command is incomplete, execute write operation for protected address and not execute internal write.

#### BP0, BP1 (Bit2, 3)

Block protection BP0 and BP1 can set up the memory address area to be protected. Refer to Table 3 for setting conditions.

| Protection level              | Status R | IS Register bit Protection area |                 |

|-------------------------------|----------|---------------------------------|-----------------|

| (Level)                       | BP1      | BP0                             | Protection area |

| all area unprotect ion<br>(0) | 0        | 0                               | nothing         |

| Upper 1/4 protection<br>(1)   | 0        | 1                               | 1800h to 1FFFh  |

| Upper 1/2 protection<br>(2)   | 1        | 0                               | 1000h to 1FFFh  |

| all area protection<br>(3)    | 1        | 1                               | 0000h to 1FFFh  |

#### Table 3: Protection level setting conditions

#### SRWP (Bit7)

Status Register Write protection SRWP protects Status Register. When "1" state and  $\overline{WP}$  pin are logic low levels, as for a Status Register Write command, they are disregarded, and as for BP0, BP1 and of a Status Register, and SRWP is protected. When  $\overline{WP}$  pin is a logic high level, a Status Register is not protected irrespective of the state of SRWP. SRWP setting conditions are shown in Table 4.

#### Table 4: SRWP setting conditions

| WP pin | SRWP | Mode                      | Status Register protection state | Protected Area | Unprotected Area |  |

|--------|------|---------------------------|----------------------------------|----------------|------------------|--|

| 1      | 0    |                           |                                  |                |                  |  |

| 0      | 0    | Software Protect<br>(SPM) | Unprotect                        | Protect        | Unprotect        |  |

| 1      | 1    |                           |                                  |                |                  |  |

| 0      | 1    | Hardware Protect<br>(HPM) | Protect                          | Protect        | Unprotect        |  |

Bit4, Bit5, Bit6 are reserve bit.

#### 3. Write Enable

Write Enable sets a Status Register WEN to "1" state. In order to perform the following operation, it is necessary to execute a Write Enable command first. A timing waveform is shown in Figure 7. Write Enable command consists of only the 1st bus cycle, OP-code is 06h.

- Write

- Status Register Write

#### 4. Write disable

Write disable sets a Status Register WEN to "0" states, and forbids an unprepared Write. Figure8 shows timing waveform. Write Enable command consists of only the 1st bus cycle. OP-code is 04h. To release from a Write disable state (WEN "0"), it should be performed the Write Enable command (06h).

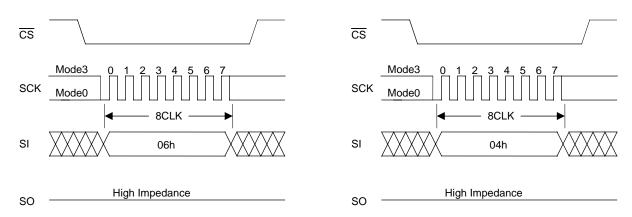

#### Figure 7: Write Enable Timing Diagram

Figure 8: Write Disable Timing Diagram

#### 5. Write

Page Write can write the arbitrary numbers of bytes of 1 to 32 bytes.

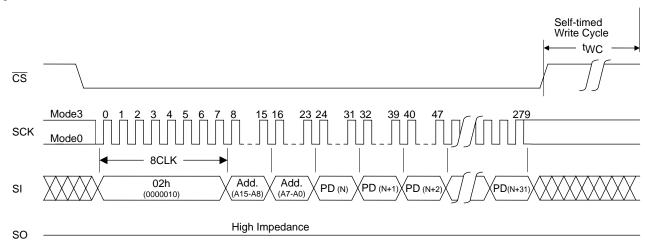

Figure9 shows timing waveform and a flow chart is shown in Figure12.

16-bit address is inputted after OP-code (02H). Then, loading is possible for write data during  $\overline{\text{CS}}$  is low. When the data loaded exceeds 32 bytes, 32 bytes loaded at the end are written.

It is necessary to load write data per byte, and when it writes by loading the data below a byte unit, a normal write is not performed. Write cycle time fixed 5ms (Max) when execute 32 bytes page write.

#### Figure 9: Write

■ A15 to A13: Don't Care

#### 6. Hold Function

HOLD pin is used in order to pause serial communication (hold state).

The timing waveform is shown in Figure10.

If  $\overline{\text{HOLD}}$  starts to falling edge in the timing SCK on a logic low level, device will be in a hold state. And if  $\overline{\text{HOLD}}$  starts to rising edge, Device will release from hold state in same timing.

Changes of  $\overline{\text{HOLD}}$  are forbidden when CLK is High level.

If it is effective when  $\overline{CS}$  is a logic low level, and when  $\overline{CS}$  is rising edged, it will release from a hold state and serial communication will be reset.

In a hold state, SO is Hi-Z, SI and SCK is Don't Care.

#### Figure 10: Hold Command Timing Diagram

#### 7. Hardware data protection

In order to prevent the unprepared writing at power-up, this device has the power-on reset function inside.

#### 8. Software data protection

To prevent unprepared operation, this device ignores the command below conditions.

- There is no the timing of rising edge of  $\overline{CS}$  during bus cycle when write command input.

- No byte unit of write data

- More than 2 bus cycles of the Status Resistor Write command input.

#### 9. Power-up

Please make CS to high to prevent a careless writing when you turn on the power supply. Please begin the command input of the read operation after 100µs (tPU\_READ) from the state to which the power-supply voltage is 2.7V or more steady.

Please begin the command input of the write operation after 10ms (tPU\_WRITE) from the state to which the power-supply voltage is 2.7V or more steady.

#### 10. Decoupling capacitor

Ceramic capacitors (0.1 $\mu$ F) must be added between VDD and VSS to each device to assure stable EEPROM operation.

#### Figure 11: Status Register Write Flow Chart

#### Figure12: Write Flow Chart

Write Enable

Write command is

Status Register Read

command is set

set

It becomes Write Disable automatically after write.

# Application Notes

#### 1) Precautions when turning on the power

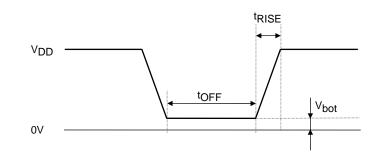

This product contains a power-on reset circuit for preventing the inadvertent writing of data when the power is turned on. The following conditions must be met in order to ensure stable operation of this circuit. No data guarantees are given in the event of an instantaneous power failure during the internal write operation.

| Parameter            | symbol            | V <sub>DD</sub> = 2.7 to 5.5V |     |     | Unit  |

|----------------------|-------------------|-------------------------------|-----|-----|-------|

| Falanciel            |                   | min                           | typ | max | Offic |

| Power rise time      | <sup>t</sup> RISE | -                             | -   | 100 | ms    |

| Power off time       | <sup>t</sup> OFF  | 10                            | -   | -   | ms    |

| Power bottom voltage | V <sub>bot</sub>  | -                             | -   | 0.2 | V     |

Notes: 1)  $\overline{\text{CS}} = \text{H}.$

## LE25CB643TT-BH

#### **ORDERING INFORMATION**

| Device         | Package                            | Shipping (Qty / Packing) |  |

|----------------|------------------------------------|--------------------------|--|

| LE25CB643TT-BH | Micro8<br>(Pb-Free / Halogen Free) | 4000 / Tape &Reel        |  |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.