# 530 MHz PLL Frequency Synthesizer LSI

### Overview

The LV2105V is a PLL frequency synthesizer Bi-CMOS LSI that provides low-voltage operation and low current drain, and that is suitable for use in a variety of radio equipment.

### **Functions**

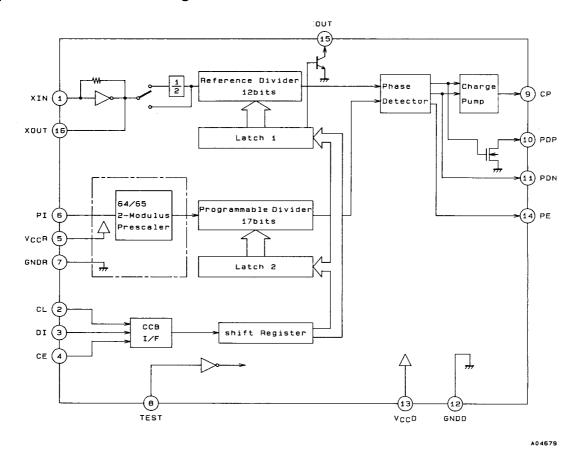

- PLL function

- Data input by serial transfer (CCB format)

- · Input amplifier for crystal oscillation circuit

- · Data output port

### **Features**

- Low operating voltage:  $(V_{CC} = 2.5 \text{ to } 5.5 \text{ V})$

- Low current drain (5.5 mA)

- Compact package (SSOP16, 0.65 mm pitch)

- VCO band switching data output port on chip

- · Data can be input while in power saving mode

- $\mbox{\ }^{\bullet}$  Data input pin high level can be input at  $V_{CC}$  or higher

- Independent setting of CP ON/OFF (high impedance) possible

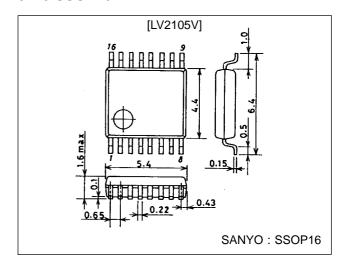

## **Package Dimensions**

unit: mm

#### 3178-SSOP16

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

# **Specifications**

#### Absolute Maximum Ratings at Ta = 25 °C

| Parameter                   | Symbol                  | Conditions                                                           | Ratings                      | Unit |

|-----------------------------|-------------------------|----------------------------------------------------------------------|------------------------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max     | V <sub>CC</sub> R, V <sub>CC</sub> D                                 | -0.3 to +6.0                 | V    |

| Maximum input valtage       | V <sub>IN</sub> max(1)  | CE, CL, DI                                                           | -0.3 to +6.0                 | V    |

| Maximum input voltage       | V <sub>IN</sub> max(2)  | XIN, TEST                                                            | -0.3 to V <sub>CC</sub> +0.3 | V    |

| Maximum output voltage      | V <sub>OUT</sub> max(1) | PDP                                                                  | -0.3 to +9.0                 | V    |

|                             | V <sub>OUT</sub> max(2) | PDN, OUT, PE                                                         | -0.3 to V <sub>CC</sub> +0.3 | V    |

| Maximum output current      | I <sub>OUT</sub> max    | PDP                                                                  | 0 to +1.0                    | mA   |

| Allowable power dissipation | Pd max                  | $114 \times 76 \times 1.6 \text{ mm}^3$ When using glass epoxy board | 230                          | mW   |

| Operating temperature       | Topr                    |                                                                      | -40 to +85                   | ۰C   |

| Storage temperature         | Tstg                    |                                                                      | -50 to +125                  | ۰C   |

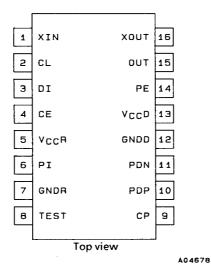

### **Pin Assignment**

Allowable Operating Ranges at  $Ta = -40 \text{ to } +85 \text{ }^{\circ}\text{C}$

| Parameter                     | Symbol              | Conditions                           | Min                  | Тур | Max  | Unit |

|-------------------------------|---------------------|--------------------------------------|----------------------|-----|------|------|

| Supply voltage                | V <sub>CC</sub>     | V <sub>CC</sub> R, V <sub>CC</sub> D | 2.5                  |     | 5.5  | V    |

| High-level input voltage      | V <sub>IH</sub>     | CE, CL, DI                           | $V_{CC}R \times 0.7$ |     | 5.5  | V    |

| Low-level input voltage       | V <sub>IL</sub>     | CE, CL, DI                           | 0                    |     | +0.6 | V    |

| Output voltage                | V <sub>OUT</sub>    | PDP                                  | 0                    |     | +7.0 | V    |

| Input frequency               | f <sub>IN</sub> (1) | XIN: Sine wave capacitive coupling   | 5                    |     | 22   | MHz  |

|                               | f <sub>IN</sub> (2) | PI: Sine wave capacitive coupling    | 100                  |     | 530  | MHz  |

| Input amplitude               | V <sub>IN</sub> (1) | XIN: Sine wave capacitive coupling   | -12                  |     | +10  | dBm  |

|                               | V <sub>IN</sub> (2) | PI: Sine wave capacitive coupling    | -18                  |     | 0    | dBm  |

| Crystal oscillation condition | Xtal                | Xtal XIN, (XOUT)                     |                      |     | 13   | MHz  |

# Electrical Characteristics at Ta = 25 $^{\circ}$ C, $V_{\rm CC}R$ = 3.0 V, $V_{\rm CC}D$ = 3.0 V

| Parameter                    | Symbol               | Conditions                               | min                  | typ  | max | Unit   |

|------------------------------|----------------------|------------------------------------------|----------------------|------|-----|--------|

|                              | V <sub>OL</sub> (1)  | PDP: I <sub>O</sub> = 0.5 mA             |                      |      | 0.5 | V      |

|                              | V <sub>OL</sub> (2)  | PDN: I <sub>O</sub> = 0.5 mA             |                      |      | 0.5 | V      |

| Low-level output voltage     | V <sub>OL</sub> (3)  | PE: I <sub>O</sub> = 0.5 mA              |                      |      | 0.5 | V      |

|                              | V <sub>OL</sub> (4)  | OUT: I <sub>O</sub> = 2.0 mA             |                      |      | 0.5 | V      |

| High lovel output voltage    | V <sub>OH</sub> (1)  | PE: $I_0 = -0.5 \text{ mA}$              | V <sub>CC</sub> -0.5 |      |     | V      |

| High-level output voltage    | V <sub>OH</sub> (2)  | PDN: $I_0 = -0.5 \text{ mA}$             | V <sub>CC</sub> -0.5 |      |     | \<br>\ |

| Output off leak current      | I <sub>OFF</sub> (1) | PDP: $V_0 = 3.0 \text{ V}$               |                      |      | 1.0 | μA     |

| Output on leak current       | I <sub>OFF</sub> (2) | CP: V <sub>O</sub> = 1.5 V               |                      |      | 100 | nA     |

| C.P output current           | I <sub>CP</sub>      | CP: V <sub>O</sub> = 1.5 V               | ±4.0                 | ±7.5 | ±11 | mA     |

|                              | I <sub>H</sub> (1)   | CE, CL, DI: V <sub>I</sub> = 3.0 V       |                      |      | 5.0 | μA     |

| High-level input current     | I <sub>H</sub> (2)   | $XIN: V_I = 3.0 V$                       | 2.3                  | 3.0  | 4.3 | μA     |

|                              | I <sub>H</sub> (3)   | TEST: $V_I = 3.0 \text{ V}$              |                      |      | 5.0 | μA     |

| Low-level input current      | I <sub>L</sub> (1)   | CE, CL, DI: $V_I = 0 \text{ V}$          |                      |      | 5.0 | μA     |

|                              | I <sub>L</sub> (2)   | $XIN: V_I = 0 V$                         | 2.3                  | 3.0  | 4.3 | μA     |

|                              | I <sub>L</sub> (3)   | TEST: V <sub>I</sub> = 0 V               |                      |      | 5.0 | μA     |

| Internal feedback resistance | Rf                   | XIN                                      |                      | 1.0  |     | MΩ     |

| Supply current               | I <sub>CC</sub> (1)  | V <sub>CC</sub> R, V <sub>CC</sub> D: *1 |                      | 5.5  | 9.0 | mA     |

| PS supply current            | I <sub>CC</sub> (2)  | V <sub>CC</sub> R, V <sub>CC</sub> D: *1 |                      | 0.4  | 0.6 | mA     |

<sup>\*1:</sup> XIN = 12.8 MHz, 10 dBm, PI = 400 MHz, 0 dBm, other input pins = 0 V, output, I/O pins = OPEN CP OFF

### **Equivalent Circuit Block Diagram**

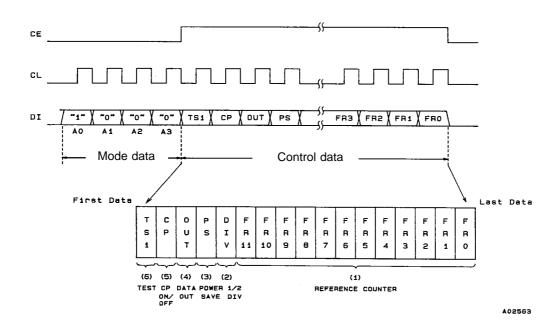

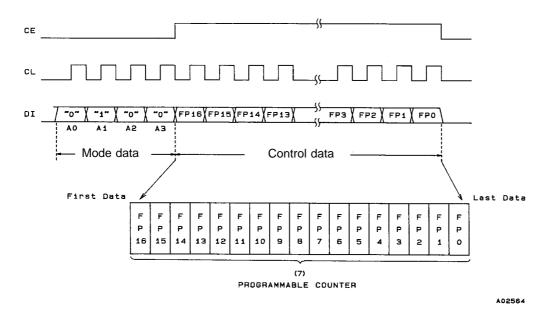

## Serial Data (PLL Control Data) Configuration

1) Mode 1: Latch-1 data (Reference divider, other data)

### 2) Mode 2: Latch-2 data (Programmable divider data)

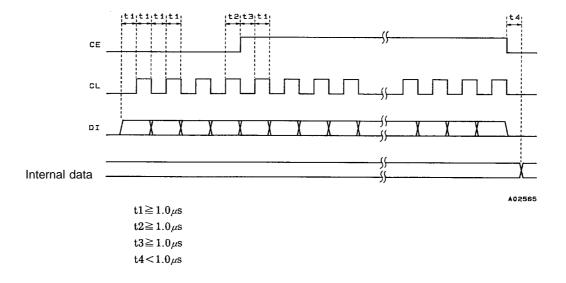

# Serial Data (Transfer) Timing

# **Serial Data Explanation**

| Pin No. | Control block/data Internal block      |                                                                                                                                                                                                                                                                              |  |  |

|---------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| (1)     | Reference frequency data<br>FR0 to FR1 | <ul> <li>Data that sets the division ratio of the reference divider.</li> <li>Binary value with FR0 as the LSB. However, the settable division ratio factor is up to 4095.</li> <li>(Actual division ratio) = (Set division ratio)</li> <li>(×2: when DIV is "1")</li> </ul> |  |  |

| (2)     | 1/2 divider data<br>DIV                | DIV data   Item   0   Through   1   1/2 DIV                                                                                                                                                                                                                                  |  |  |

Continued on next page.

# LV2105V

Continued from preceding page.

| Pin No. | Control block/data                       | Internal block                                                                                                                                                                             |

|---------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (3)     | Power save data<br>PS                    | Data that sets the power save mode on or off      PS data                                                                                                                                  |

| (4)     | Output port data<br>OUT                  | Data that sets the output of the output port  OUT data OUT Pin  0 Low  1 High                                                                                                              |

| (5)     | Charge pump ON/OFF data<br>CP            | Data that sets whether to operate the charge pump or to implement high impedance.  CP data                                                                                                 |

| (6)     | LSI test data TS1                        | <ul> <li>LSI test mode switch.</li> <li>Set TS1 = 0. Normally, the TEST pin is connected to GND.</li> </ul>                                                                                |

| (7)     | Programmable divider data<br>FP0 to FP16 | <ul> <li>Data that sets the division ratio of the programmable divider.</li> <li>Binary value with FP0 as the LSB. However, the settable division ratio factor is up to 131071.</li> </ul> |

# **Pin Functions**

|    | Pin Name          | Pin Function                                                                            | I/O Style                   |

|----|-------------------|-----------------------------------------------------------------------------------------|-----------------------------|

| 1  | XIN               | Reference signal input pin (Xtal oscillation pin)                                       | CMOS input                  |

| 2  | CL                | Data input pin                                                                          | CMOS, No pull-down          |

| 3  | DI                | Data input pin                                                                          | CMOS, No pull-down          |

| 4  | CE                | Data input pin                                                                          | CMOS, No pull-down          |

| 5  | V <sub>CC</sub> R | ECL block power supply pin                                                              |                             |

| 6  | PI                | Comparison signal input pin                                                             | BIP input                   |

| 7  | GND R             | ECL block GND pin                                                                       |                             |

| 8  | TEST              | LSI test pin. Must be connected to GND.                                                 | CMOS, No pull-down          |

| 9  | СР                | Built-in charge pump output pin                                                         | BIP                         |

| 10 | PDP               | Phase comparator output for an external charge pump. If not to be used, connect to GND. | CMOS, Nch open-drain output |

| 11 | PDN               | Phase comparator output for an external charge pump.                                    | CMOS output                 |

| 12 | GND D             | GND pin for circuits except the ECL block                                               |                             |

| 13 | V <sub>CC</sub> D | Power supply pin for circuits except the ECL block                                      |                             |

| 14 | PE                | Phase error output pin for phase comparator CMOS output                                 |                             |

| 15 | OUT               | Output port pin for switching external SW. BIP NPN open-collector o                     |                             |

| 16 | XOUT              | Output pin for Xtal oscillation CMOS output                                             |                             |

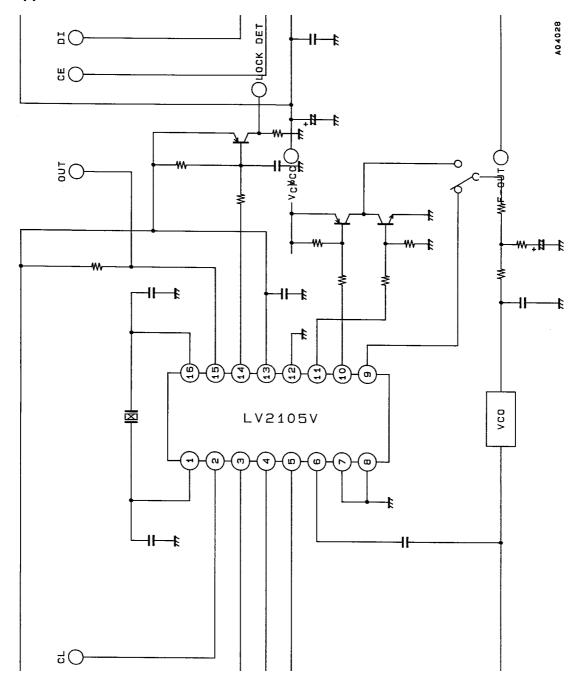

# **Sample Application Circuit**

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1995. Specifications and information herein are subject to change without notice.