SCBS686A - APRIL 1997 - REVISED DECEMBER 1999

- Members of the Texas Instruments (TI™) Broad Family of Testability Products Supporting IEEE Std 1149.1-1990 (JTAG) Test Access Port (TAP) and Boundary-Scan Architecture

- Extend Scan Access From Board Level to Higher Levels of System Integration

- Promote Reuse of Lower-Level (Chip/Board) Tests in System Environment

- While Powered at 3.3 V, Both the Primary and Secondary TAPs Are Fully 5-V Tolerant for Interfacing to 5-V and/or 3.3-V Masters and Targets

- Switch-Based Architecture Allows Direct Connect of Primary TAP to Secondary TAP

- Primary TAP Is Multidrop for Minimal Use of Backplane Wiring Channels

- Shadow Protocols Can Occur in Any of Test-Logic-Reset, Run-Test/Idle, Pause-DR, and Pause-IR TAP States to Provide for Board-to-Board Test and Built-In Self-Test

| SN54LVT8<br>SN74LVT8996 |    | OR F |                 |

|-------------------------|----|------|-----------------|

| A4 [                    |    | 24   | A5              |

| A3 [                    | 2  | 23   | A6              |

| A2 [                    | 3  | 22   | A7              |

| A1 [                    | 4  | 21   | A8              |

| A0 [                    | 5  | 20   | A9              |

| BYP [                   | 6  | 19   | V <sub>CC</sub> |

| GND [                   | 7  | 18   | CON             |

| PTDO [                  | 8  | 17   | STDI            |

| PTCK [                  | 9  | 16   | STCK            |

| PTMS [                  | 10 | 15   | STMS            |

| PTDI [                  | 11 | 14   | STDO            |

| PTRST [                 | 12 | 13   | STRST           |

- Simple Addressing (Shadow) Protocol Is Received/Acknowledged on Primary TAP

- 10-Bit Address Space Provides for up to 1021 User-Specified Board Addresses

- Bypass (BYP) Pin Forces Primary-to-Secondary Connection Without Use of Shadow Protocols

- Connect (CON) Pin Provides Indication of Primary-to-Secondary Connection

- High-Drive Outputs (–32-mA I<sub>OH</sub>, 64-mA I<sub>OL</sub>) Support Backplane Interface at Primary and High Fanout at Secondary

- Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

- ESD Protection Exceeds JESD 22

2000-V Human-Body Model (A114-A)

- 200-V Machine Model (A115-A)

- 1000-V Charged-Device Model (C101)

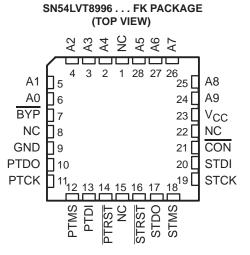

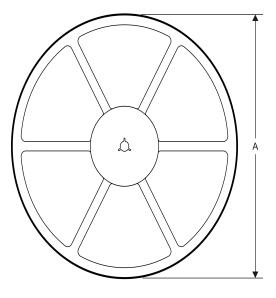

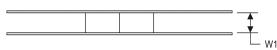

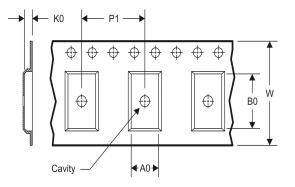

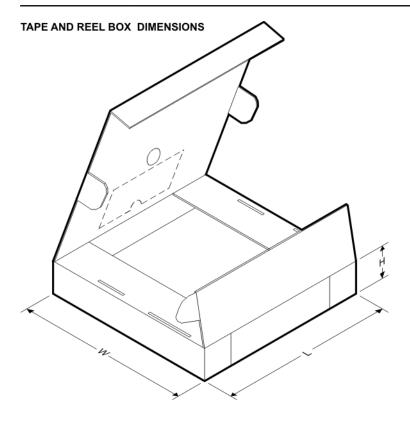

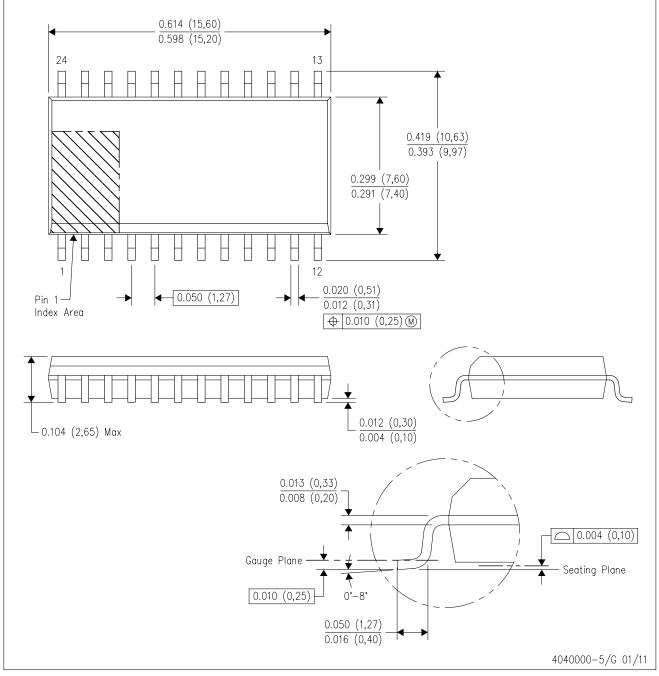

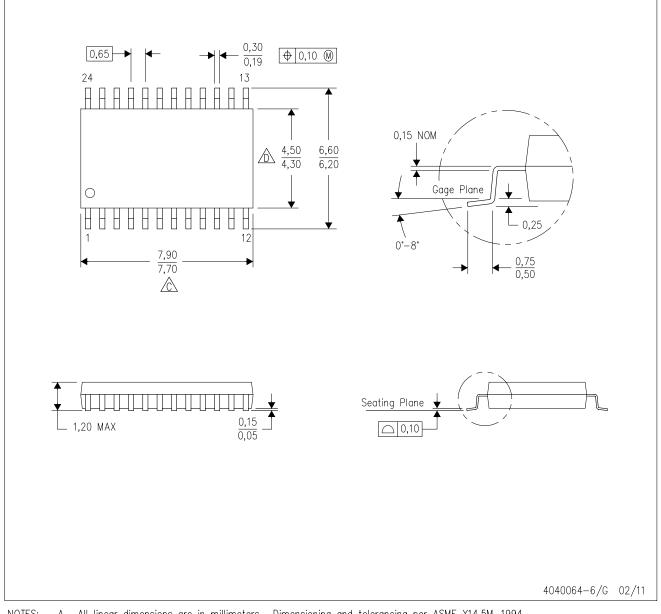

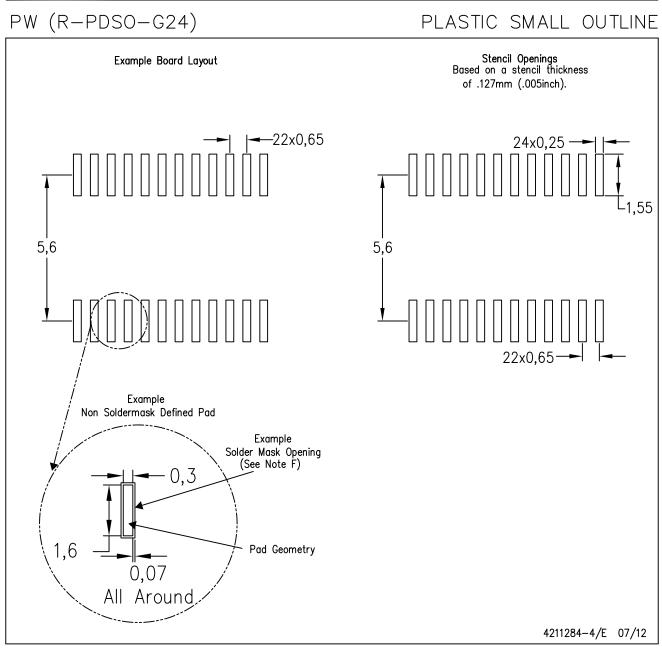

- Package Options Include Plastic Small-Outline (DW) and Thin Shrink Small-Outline (PW) Packages, Ceramic Chip Carriers (FK), and Ceramic DIPs (JT)

NC - No internal connection

## description

The 'LVT8996 10-bit addressable scan ports (ASP) are members of the Texas Instruments SCOPE<sup>™</sup> testability integrated-circuit family. This family of devices supports IEEE Std 1149.1-1990 boundary scan to facilitate testing of complex circuit assemblies. Unlike most SCOPE<sup>™</sup> devices, the ASP is not a boundary-scannable device, rather, it applies TI's addressable-shadow-port technology to the IEEE Std 1149.1-1990 (JTAG) test access port (TAP) to extend scan access beyond the board level.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SCOPE and TI are trademarks of Texas Instruments Incorporated.

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999, Texas Instruments Incorporated

## SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCB5686A – APRIL 1997 – REVISED DECEMBER 1999

### description (continued)

These devices are functionally equivalent to the 'ABT8996 ASPs. Additionally, they are designed specifically for low-voltage (3.3-V)  $V_{CC}$  operation, but with the capability to interface to 5-V masters and/or targets.

Conceptually, the ASP is a simple switch that can be used to directly connect a set of multidrop primary TAP signals to a set of secondary TAP signals – for example, to interface backplane TAP signals to a board-level TAP. The ASP provides all signal buffering that might be required at these two interfaces. When primary and secondary TAPs are connected, only a moderate propagation delay is introduced – no storage/retiming elements are inserted. This minimizes the need for reformatting board-level test vectors for in-system use.

Most operations of the ASP are synchronous to the primary test clock (PTCK) input. PTCK is always buffered directly onto the secondary test clock (STCK) output.

Upon power up of the device, the ASP assumes a condition in which the primary TAP is disconnected from the secondary TAP (unless the bypass signal is used, as below). This reset condition also can be entered by the assertion of the primary test reset (PTRST) input or by use of shadow protocol. PTRST is always buffered directly onto the secondary test reset (STRST) output, ensuring that the ASP and its associated secondary TAP can be reset simultaneously.

When connected, the primary test data input (PTDI) and primary test mode select (PTMS) input are buffered onto the secondary test data output (STDO) and secondary test mode select (STMS) output, respectively, while the secondary test data input (STDI) is buffered onto the primary test data output (PTDO). When disconnected, STDO is at high impedance, while PTDO is at high impedance, except during acknowledgment of a shadow protocol. Upon disconnect of the secondary TAP, STMS holds its last low or high level, allowing the secondary TAP to be held in its last stable state. Upon reset of the ASP, STMS is high, allowing the secondary TAP to be synchronously reset to the Test-Logic-Reset state.

In system, primary-to-secondary connection is based on shadow protocols that are received and acknowledged on PTDI and PTDO, respectively. These protocols can occur in any of the stable TAP states other than Shift-DR or Shift-IR (i.e., Test-Logic-Reset, Run-Test/Idle, Pause-DR or Pause-IR). The essential nature of the protocols is to receive/transmit an address via a serial bit-pair signaling scheme. When an address is received serially at PTDI that matches that at the parallel address inputs (A9–A0), the ASP serially retransmits its address at PTDO as an acknowledgment and then assumes the connected (ON) status, as above. If the received address does not match that at the address inputs, the ASP immediately assumes the disconnected (OFF) status without acknowledgment.

The ASP also supports three dedicated addresses that can be received globally (that is, to which all ASPs respond) during shadow protocols. Receipt of the dedicated disconnect address (DSA) causes the ASP to disconnect in the same fashion as a nonmatching address. Reservation of this address for global use ensures that at least one address is available to disconnect all receiving ASPs. The DSA is especially useful when the secondary TAPs of multiple ASPs are to be left in different stable states. Receipt of the reset address (RSA) causes the ASP to assume the reset condition, as above. Receipt of the test-synchronization address (TSA) causes the ASP to assume a connect status (MULTICAST) in which PTDO is at high impedance but the connections from PTMS to STMS and PTDI to STDO are maintained to allow simultaneous operation of the secondary TAPs of multiple ASPs. This is useful for multicast TAP-state movement, simultaneous test operation (such as in Run-Test/Idle state), and scanning of common test data into multiple like scan chains. The TSA is valid only when received in the Pause-DR or Pause-IR TAP states.

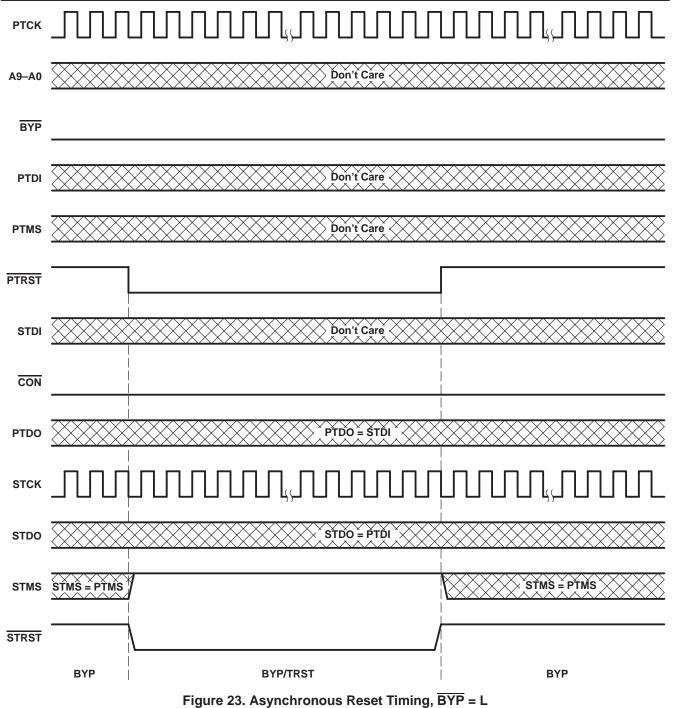

Alternatively, primary-to-secondary connection can be selected by assertion of a low level at the bypass ( $\overline{BYP}$ ) input. This operation is asynchronous to PTCK and is independent of PTRST and/or power-up reset. This bypassing feature is especially useful in the board-test environment, since it allows the board-level automated test equipment (ATE) to treat the ASP as a simple transceiver. When the  $\overline{BYP}$  input is high, the ASP is free to respond to shadow protocols. Otherwise, when  $\overline{BYP}$  is low, shadow protocols are ignored.

### description (continued)

Whether the connected status is achieved by use of shadow protocol or by use of  $\overline{\text{BYP}}$ , this status is indicated by a low level at the connect ( $\overline{\text{CON}}$ ) output. Likewise, when the secondary TAP is disconnected from the primary TAP, the  $\overline{\text{CON}}$  output is high.

The SN54LVT8996 is characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C. The SN74LVT8996 is characterized for operation from  $-40^{\circ}$ C to  $85^{\circ}$ C.

|     | FUNCTION TABLE |                         |         |      |                     |      |      |     |                       |  |

|-----|----------------|-------------------------|---------|------|---------------------|------|------|-----|-----------------------|--|

| INF | PUTS           | SHADOW-PROTOCOL         | OUTPUTS |      |                     |      |      |     | PRIMARY-TO-SECONDARY  |  |

| BYP | PTRST          | RESULT <sup>†</sup>     | STRST   | STCK | STMS                | STDO | PTDO | CON | CONNECT STATUS        |  |

| L   | L              | —                       | L       | PTCK | H‡                  | PTDI | STDI | L   | BYP/TRST <sup>‡</sup> |  |

| L   | Н              | —                       | н       | PTCK | PTMS                | PTDI | STDI | L   | BYP                   |  |

| н   | L              | —                       | L       | PTCK | Н                   | Z    | Z    | Н   | TRST                  |  |

| н   | Н              | RESET                   | н       | PTCK | Н                   | Z    | Z    | Н   | RESET                 |  |

| н   | Н              | MATCH                   | н       | PTCK | PTMS                | PTDI | STDI | L   | ON                    |  |

| н   | Н              | NO MATCH                | Н       | PTCK | STMS <sub>0</sub> § | Z    | Z    | Н   | OFF                   |  |

| н   | Н              | HARD ERROR <sup>¶</sup> | н       | PTCK | STMS0§              | Z    | Z    | Н   | OFF                   |  |

| н   | Н              | DISCONNECT              | н       | PTCK | STMS <sub>0</sub> § | Z    | Z    | Н   | OFF                   |  |

| н   | Н              | TEST SYNCHRONIZATION    | Н       | PTCK | PTMS                | PTDI | Z    | L   | MULTICAST             |  |

<sup>+</sup> Shadow protocols are received serially via PTCK and PTDI and acknowledged serially via PTCK and PTDO under certain conditions in which PTMS is static low or static high (see shadow protocol). The result shown here follows any required acknowledgment.

In normal operation of IEEE Std 1149.1-compliant architectures, it is recommended that TMS be high prior to release of TRST. The BYP/TRST connect status ensures that this condition is met at STMS regardless of the applied PTMS. Also, it is recommended that STMS be kept high for a minimum duration of 5 PTCK cycles following assertion of PTRST, either by maintaining PTRST low or by setting PTMS high. This ensures that ICs both with and without TRST inputs are moved to their Test-Logic-Reset TAP states. It is expected that in normal application, this condition occurs only when BYP is fixed at the low state. In such case, upon release of PTRST, the ASP immediately resumes the BYP connect status. § STMS level before indicated steady-state conditions were established

The shadow protocol is well defined. Some variations in the protocol are tolerated (see protocol errors). Those that are not tolerated produce protocol result HARD ERROR and cause disconnect as indicated.

# SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCBS686A – APRIL 1997 – REVISED DECEMBER 1999

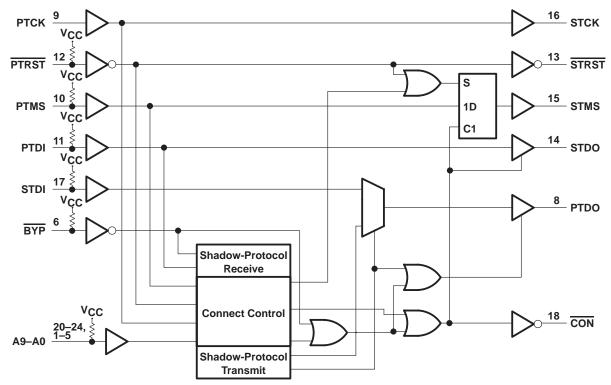

### functional block diagram

Pin numbers shown are for the DW, JT, and PW packages.

SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCB5686A – APRIL 1997 – REVISED DECEMBER 1999

### **Terminal Functions**

| TERMINAL<br>NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A9–A0            | Address inputs. The ASP compares addresses received via shadow protocol against the value at A9–A0 to determine address match. The bit order is from most significant to least significant. An internal pullup at each A9–A0 terminal forces the terminal to a high level if it has no external connection.                                                                                                                                                                                                                                                                                                                                                                            |

| BYP              | Bypass input. A low input at BYP forces the ASP into BYP or BYP/TRST status, depending on PTRST being high or low, respectively. While BYP is low, shadow protocols are ignored. Otherwise, while BYP is high, the ASP is free to respond to shadow protocols. An internal pullup forces BYP to a high level if it has no external connection.                                                                                                                                                                                                                                                                                                                                         |

| CON              | Connect indicator (out <u>put).</u> The ASP indicates secondary-scan-port activity (resulting from BYP, BYP/TRST, MULTICAST, or ON status) by forcing CON to be low. Inactivity (resulting from OFF, RESET, or TRST status) is indicated when CON is high.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND              | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PTCK             | Primary test clock. PTCK receives the TCK signal required by IEEE Std 1149.1-1990. The ASP always buffers PTCK to STCK. Shadow protocols are received/acknowledged synchronously to PTCK and connect-status changes invoked by shadow protocol are made synchronously to PTCK.                                                                                                                                                                                                                                                                                                                                                                                                         |

| PTDI             | Primary test data input. PTDI receives the TDI signal required by IEEE Std 1149.1-1990. During appropriate TAP states, the ASP monitors PTDI for shadow protocols. During shadow protocols, data at PTDI is captured on the rising edge of PTCK. When a valid shadow protocol is received in this fashion, the ASP compares the received address against the A9–A0 inputs. If the ASP detects a match, it outputs an acknowledgment and then connects its primary TAP terminals to its secondary TAP terminals. Under BYP, BYP/TRST, MULTICAST or ON status, the ASP buffers the PTDI signal to STDO. An internal pullup forces PTDI to a high level if it has no external connection. |

| PTDO             | Primary test data output. PTDO transmits the TDO signal required by IEEE Std 1149.1-1990. During shadow protocols, the ASP transmits any required acknowledgment via the PTDO. The acknowledgment data output at PTDO changes on the falling edge of PTCK. Under BYP, BYP/TRST, or ON status, the ASP buffers the PTDO signal from STDI. Under OFF, MULTICAST, RESET, or TRST status, PTDO is at high impedance.                                                                                                                                                                                                                                                                       |

| PTMS             | Primary test mode select. PTMS receives the TMS signal required by IEEE Std 1149.1-1990. The ASP monitors the PTMS to determine the TAP-controller state. During stable TAP states other than Shift-DR or Shift-IR (i.e., Test-Logic-Reset, Run-Test-Idle, Pause-DR, Pause-IR) the ASP can respond to shadow protocols. Under BYP, MULTICAST, or ON status, the ASP buffers the PTMS signal to STMS. An internal pullup forces PTMS to a high level if it has no external connection.                                                                                                                                                                                                  |

| PTRST            | Primary test reset. PTRST receives the TRST signal allowed by IEEE Std 1149.1-1990. The ASP always buffers PTRST to STRST. A low input at PTRST forces the ASP to assume TRST or BYP/TRST status, depending on BYP being high or low, respectively. Such operation also asynchronously resets the internal ASP state to its power-up condition. Otherwise, while PTRST is high, the ASP is free to respond to shadow protocols. An internal pullup forces PTRST to a high level if it has no external connection.                                                                                                                                                                      |

| STCK             | Secondary test clock. STCK retransmits the TCK signal required by IEEE Std 1149.1-1990. The ASP always buffers STCK from PTCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| STDI             | Secondary test data input. STDI receives the TDI signal required by IEEE Std 1149.1-1990. Under BYP, BYP/TRST, or ON status, the ASP buffers STDI to PTDO. An internal pullup forces STDI to a high level if it has no external connection.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| STDO             | Secondary test data output. STDO transmits the TDO signal required by IEEE Std 1149.1-1990. Under BYP, BYP/TRST, MULTICAST, or ON status, the ASP buffers STDO from PTDI. Under OFF, RESET, or TRST status, STDO is at high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| STMS             | Secondary test mode select. STMS retransmits the TMS signal required by IEEE Std 1149.1-1990. Under BYP, MULTICAST, or ON status, the ASP buffers STMS from PTMS. When disconnected (as a result of OFF status), STMS maintains its last valid state until the ASP assumes BYP/TRST, RESET, or TRST status (upon which it is forced high) or the ASP again assumes BYP, MULTICAST, or ON status.                                                                                                                                                                                                                                                                                       |

| STRST            | Secondary test reset. STRST retransmits the TRST signal allowed by IEEE Std 1149.1-1990. The ASP always buffers STRST from PTRST.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCC              | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCBS686A - APRIL 1997 - REVISED DECEMBER 1999

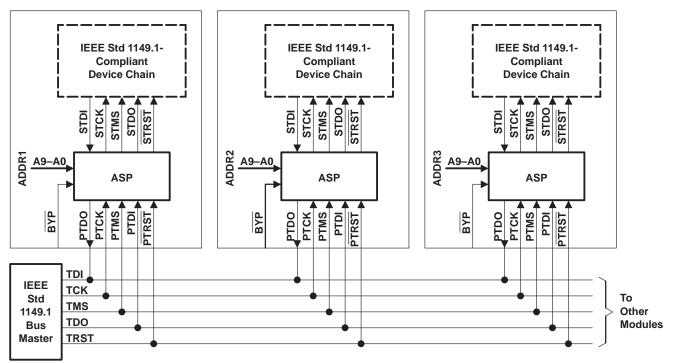

### application information

In application, the ASP is used at each of several (serially-chained) groups of IEEE Std 1149.1-compliant devices. The ASP for each such group is assigned an address (via inputs A9-A0) that is unique from that assigned to ASPs for the remaining groups. Each ASP is wired at its primary TAP to common (multidrop) TAP signals (sourced from a central IEEE Std 1149.1 bus master) and fans out its secondary TAP signals to the specific group of IEEE Std 1149.1-compliant devices with which it is associated. An example is shown in Figure 1.

This application allows the ASP to be wired to a 4- or 5-wire multidrop test access bus, such as might be found on a backplane. Each ASP would then be located on a module, for example a printed-circuit board (PCB), that contains a serial chain of IEEE Std 1149.1-compliant devices and that would plug into the module-to-module bus (e.g., backplane). In the complete system, the ASP shadow protocols would allow the selection of the scan chain on a single module. The selected scan chain could then be controlled, via the multidrop TAP, as if it were the only scan chain in the system. Normal IR and DR scans can then be performed to accomplish the module test objectives.

Once scan operations to a given module are complete, another module can be selected in the same fashion, at which time the ASP-based connection to the first module is dissolved. This procedure can be continued progressively for each module to be tested. Finally, one of two global addresses can be issued to either leave all modules unselected (disconnect address, DSA) or to deselect and reset scan chains for all modules (reset address, RSA).

Additionally, in Pause-DR and Pause-IR TAP states, a third global address (test-synchronization address, TSA) can be invoked to allow simultaneous TAP-state changes and multicast scan-in operations to selected modules. This is especially useful in the former case, for allowing selected modules to be moved simultaneously to the Run-Test-Idle TAP state for module-level or module-to-module built-in self-test (BIST) functions, which operate synchronously to TCK in that TAP state, and in the latter case, for scanning common test setup/data into multiple like modules.

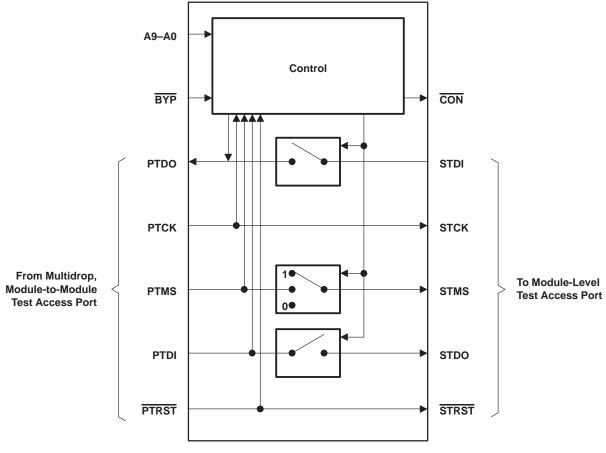

### architecture

Conceptually, the ASP can be viewed as a bank of switches that can connect or isolate a module-level TAP to/from a higher-level (e.g., module-to-module) TAP. This is shown in Figure 2. The state of the switches (open versus closed) is based on shadow protocols, which are received on PTDI and are synchronous to PTCK.

The simple architecture of the ASP allows the system designer to overcome the limitations of IEEE Std 1149.1 *ring* and *star* configurations. Ring configurations (in which each module's TDO is chained to the next module's TDI) are of limited use in backplane environments, since removal of a module breaks the scan chain and prevents test of the remainder of the system. Star configurations (in which all module TDOs and TDIs are connected in parallel) are suited to the backplane environment, but, since each module must receive its own TMS, are costly in terms of backplane routing channels. By comparison, use of the ASP allows all five IEEE Std 1149.1 signals to be routed in multidrop fashion.

Figure 2. ASP Conceptual Model

As shown in the functional block diagram, the ASP comprises three major logic blocks. Blocks for shadow-protocol receive and shadow-protocol transmit are responsible for receipt of select protocol and transmission of acknowledge protocol, respectively. The connect-control block is responsible for TAP-state monitor and address matching.

Some additional logic is illustrated outside of these major blocks. This additional logic is responsible for controlling the activity of the ASP outputs based on the shadow-protocol result and/or protocol bypass [as selected by an active (low)  $\overline{\text{BYP}}$  input].

SCBS686A - APRIL 1997 - REVISED DECEMBER 1999

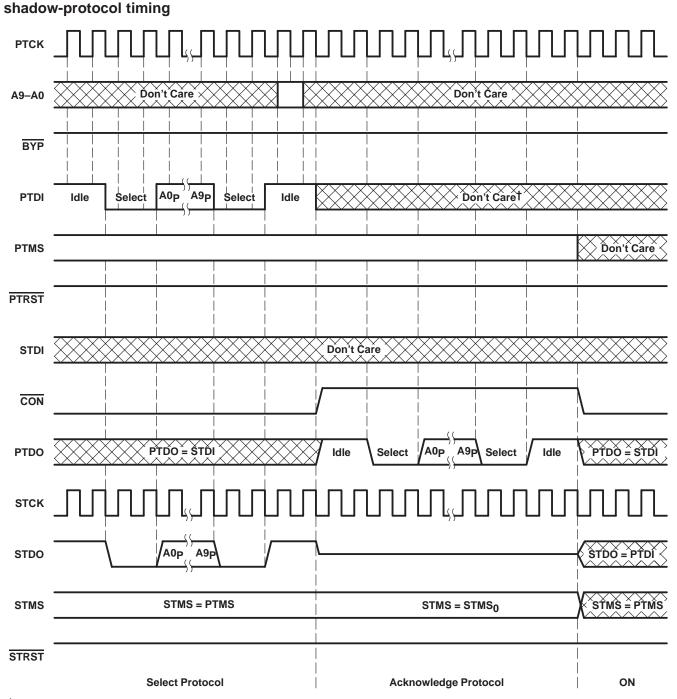

### shadow protocol

Addressing of an ASP in system is accomplished by shadow protocols, which are received at PTDI synchronously to PTCK. Shadow protocols can occur only in the following stable TAP states: Test-Logic-Reset, Run-Test/Idle, Pause-DR, and Pause-IR. Shadow protocols never occur in Shift-DR or Shift-IR states to prevent contention on the signal bus to which PTDO is wired. Additionally, the ASP PTMS must be held at a constant low or high level throughout a shadow protocol. If TAP-state changes occur in the midst of a shadow protocol. the shadow protocol is aborted and the select-protocol state machine returns to its initial state.

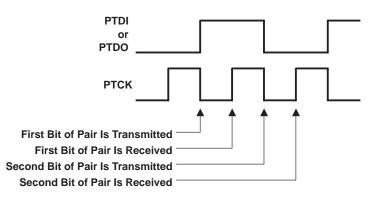

The shadow protocol is based on a serial bit-pair signaling scheme in which two bit-pair combinations (data one, data zero) are used to represent address data and the other two bit-pair combinations (select, idle) are used for framing – that is, to indicate where address data begins and ends.

These bit pairs are received serially at PTDI (or transmitted serially at PTDO) synchronously to PTCK as follows:

- The idle bit pair (I) is represented as two consecutive high signals.

- The select bit pair (S) is represented as two consecutive low signals.

- The data-one bit pair (D) is represented as a low signal followed by a high signal.

- The data-zero bit pair (D) is represented as a high signal followed by a low signal.

Figure 3. Bit-Pair Timing (Data Zero Shown)

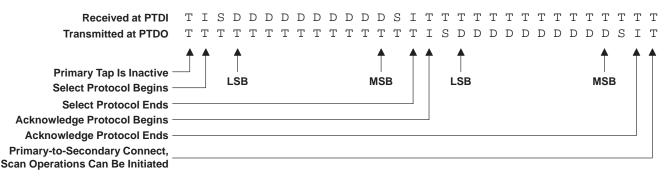

A complete shadow protocol is composed of the receipt of a select protocol followed, if applicable, by the transmission of an acknowledge protocol (which is issued from PTDO only if the received address matches that at the A9–A0 inputs). Both of these subprotocols are composed of ten data bit pairs framed at the beginning by idle and select bit pairs and at the end by select and idle bit pairs. This is represented in an abbreviated fashion as follows: ISDDDDDDDDDDSI. Figure 4 shows a complete shadow protocol (the symbol T is used to represent a high-impedance condition on the associated signal line - since the high-impedance state at PTDI is logically high due to pullup, it maps onto the idle bit pair).

Figure 4. Complete Shadow Protocol

#### select protocol

The select protocol is the ASP's means of receiving (at PTDI) address information from an IEEE Std 1149.1 bus master. It follows the ISDDDDDDDDDDDSI sequence described previously. A 10-bit address value is decoded from the received data-one and/or data-zero bit pairs. These bit pairs are interpreted in least-significant-bit-first order (that is, the first data bit pair received is considered to correspond to A0).

#### acknowledge protocol

Following the receipt of a complete select-protocol sequence, the protocol result provisionally is set to NO MATCH and the connect status set to OFF. The received address is then compared to that at the ASP address inputs (A9–A0). If these address values match, the ASP immediately (with no delay) responds with an acknowledge protocol transmitted from PTDO. This protocol follows the ISDDDDDDDDDDDSI sequence described previously. The transmitted address represents the address of the selected ASP which, by definition, is the same address the ASP received in the select protocol. The 10-bit address value is encoded into data-one and/or data-zero bit pairs. The bit pairs are to be interpreted in least-significant-bit-first order (that is, the first data bit pair transmitted is to be considered to correspond to A0). If the received address does not match that at the A9–A0 inputs, no acknowledge protocol is transmitted and the shadow protocol is considered complete.

#### protocol errors

Protocol errors occur when bit pairs are received out of sequence. Some of these sequencing errors can be tolerated and produce protocol result SOFT ERROR – no specific action occurs as a result. Other errors represent cases where the addressing information could be incorrectly received and produce protocol result HARD ERROR – these are characterized by sequences in which at least one bit of address data has been properly transmitted, followed by a sequencing error; when protocol result HARD ERROR occurs, any connection to an ASP is dissolved.

Table 1 lists the bit-pair sequences that produce protocol results SOFT ERROR and HARD ERROR. A hard error also results when the primary TAP state changes during select protocol following the proper transmission of at least one bit of address data. Figures 16 and 17 show shadow-protocol timing in case of protocol result HARD ERROR while Figure 18 shows shadow-protocol timing in case of protocol result SOFT ERROR.

| SOFT ERROR   | HARD ERROR               |

|--------------|--------------------------|

| I(D)I        |                          |

| I(D)(S)I     |                          |

| I(D)(S)(D)I  | IS(D)I                   |

| I(S)I        | IS(D)S(D)I<br>IS(D)S(S)I |

| IS(S)(D)I    |                          |

| IS(S)(D)(S)I |                          |

Table 1. Shadow-Protocol Errors<sup>†</sup>

A bit-pair token in parentheses represents one or more instances.

### long address

Receipt of an address longer than ten bits produces protocol result HARD ERROR and the ASP assumes OFF status. The sole exceptions are when all data ones are received or all data zeros are received. In these special cases, the global addresses represented by these bit sequences are observed and appropriate action taken. That is, in the case that only data ones (ten or more) are received, the shadow-protocol result is TEST SYNCHRONIZATION (if the primary TAP state is Pause-DR or Pause-IR), and in the case that only data zeros (ten or more) are received, the shadow-protocol result is RESET (see test-synchronization address and reset address).

## SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCBS686A - APRIL 1997 - REVISED DECEMBER 1999

### short address

In all cases, receipt of an address shorter than ten bits produces protocol result HARD ERROR and the ASP assumes OFF status.

### connect control

The connect-control block monitors the primary TAP state to enable receipt/acknowledge of shadow protocols in appropriate states (namely, the stable, non-Shift TAP states: Test-Logic-Reset, Run-Test/Idle, Pause-DR, and Pause-IR). Upon receipt of a valid shadow protocol, this block performs the address matching required to compute the shadow-protocol result.

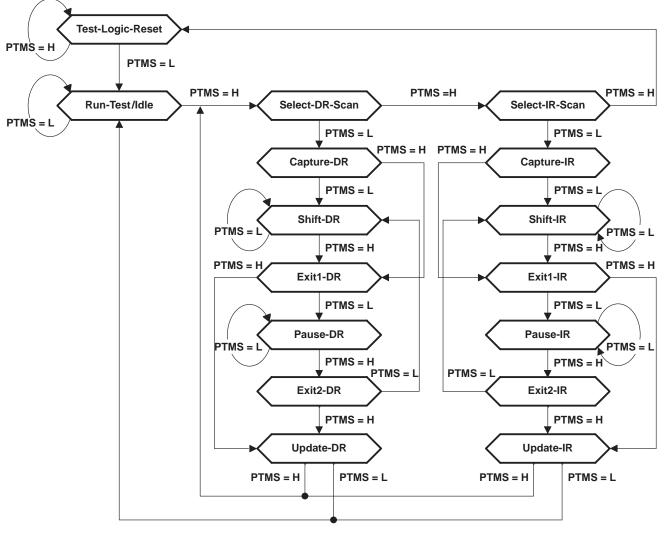

### **TAP-state monitor**

The TAP-state monitor is a synchronous finite-state machine that monitors the primary TAP state. The state diagram is shown in Figure 5 and mirrors that specified by IEEE Std 1149.1-1990. The TAP-state monitor proceeds through its states based on the level of PTMS at the rising edge of PTCK. Each state is described both in terms of its significance for ASP devices and for connected IEEE Std 1149.1-compliant devices (called targets). However, the monitor state (primary TAP) can be different from that of disconnected scan chains (secondary TAP).

Figure 5. TAP-Monitor State Diagram

### SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCB5666A – APRIL 1997 – REVISED DECEMBER 1999

#### Test-Logic-Reset

The ASP TAP-state monitor powers up in the Test-Logic-Reset state. Alternatively, the ASP can be forced asynchronously to this state by assertion of its PTRST input. In the stable Test-Logic-Reset state, the ASP is enabled to receive and respond to shadow protocols. The ASP does not recognize the TSA in this state.

For a target device in the stable Test-Logic-Reset state, the test logic is reset and is disabled so that the normal logic function of the device is performed. The instruction register is reset to an opcode that selects the optional IDCODE instruction, if supported, or the BYPASS instruction. Certain data registers also can be reset to their power-up values.

#### Run-Test/Idle

In the stable Run-Test/Idle state, the ASP is enabled to receive and respond to shadow protocols. The ASP does not recognize the TSA in this state.

For a target device, Run-Test/Idle is a stable state in which the test logic can be actively running a test or can be idle.

#### Select-DR-Scan, Select-IR-Scan

The ASP is not enabled to receive and respond to shadow protocols in the Select-DR-Scan and Select-IR-Scan states.

For a target device, no specific function is performed in the Select-DR-Scan and Select-IR-Scan states, and the TAP controller exits either of these states on the next TCK cycle. These states allow the selection of either data-register scan or instruction-register scan.

#### Capture-DR

The ASP is not enabled to receive and respond to shadow protocols in the Capture-DR state.

For a target device in the Capture-DR state, the selected data register can capture a data value as specified by the current instruction. Such capture operations occur on the rising edge of TCK, upon which the Capture-DR state is exited.

### Shift-DR

The ASP is not enabled to receive and respond to shadow protocols in the Shift-DR state.

For a target device, upon entry to the Shift-DR state, the selected data register is placed in the scan path between TDI and TDO, and on the first falling edge of TCK, TDO goes from the high-impedance state to an active state. TDO outputs the logic level present in the least-significant bit of the selected data register. While in the stable Shift-DR state, data is serially shifted through the selected data register on each TCK cycle.

#### Exit1-DR, Exit2-DR

The ASP is not enabled to receive and respond to shadow protocols in the Exit1-DR and Exit2-DR states.

For a target device, the Exit1-DR and Exit2-DR states are temporary states that end a data-register scan. It is possible to return to the Shift-DR state from either Exit1-DR or Exit2-DR without recapturing the data register. On the first falling edge of TCK after entry to Exit1-DR, TDO goes from the active state to the high-impedance state.

#### Pause-DR

In the stable Pause-DR state, the ASP is enabled to receive and respond to shadow protocols. Additionally, the TSA can be recognized in this state.

For target devices, no specific function is performed in the stable Pause-DR state. The Pause-DR state suspends and resumes data-register scan operations without loss of data.

# SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCBS686A – APRIL 1997 – REVISED DECEMBER 1999

### Update-DR

The ASP is not enabled to receive and respond to shadow protocols in the Update-DR state.

For a target device, if the current instruction calls for the selected data register to be updated with current data, such update occurs on the falling edge of TCK, following entry to the Update-DR state.

### Capture-IR

The ASP is not enabled to receive and respond to shadow protocols in the Capture-IR state.

For a target device in the Capture-IR state, the instruction register captures its current status value. This capture operation occurs on the rising edge of TCK, upon which the Capture-IR state is exited.

### Shift-IR

The ASP is not enabled to receive and respond to shadow protocols in the Shift-IR state.

For a target device, upon entry to the Shift-IR state, the instruction register is placed in the scan path between TDI and TDO, and on the first falling edge of TCK, TDO goes from the high-impedance state to an active state. TDO outputs the logic level present in the least-significant bit of the instruction register. While in the stable Shift-IR state, instruction data is serially shifted through the instruction register on each TCK cycle.

### Exit1-IR, Exit2-IR

The ASP is not enabled to receive and respond to shadow protocols in the Exit1-IR and Exit2-IR states.

For target devices, the Exit1-IR and Exit2-IR states are temporary states that end an instruction-register scan. It is possible to return to the Shift-IR state from either Exit1-IR or Exit2-IR without recapturing the instruction register. On the first falling edge of TCK after entry to Exit1-IR, TDO goes from the active state to the high-impedance state.

#### Pause-IR

In the stable Pause-IR state, the ASP is enabled to receive and respond to shadow protocols. Additionally, the TSA can be recognized in this state.

For target devices, no specific function is performed in the stable Pause-IR state, in which the TAP controller can remain indefinitely. The Pause-IR state suspends and resumes instruction-register scan operations without loss of data.

### Update-IR

The ASP is not enabled to receive and respond to shadow protocols in the Update-IR state.

For target devices, the current instruction is updated and takes effect on the falling edge of TCK, following entry to the Update-IR state.

### SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCB5666A – APRIL 1997 – REVISED DECEMBER 1999

### address matching

Connect status of the ASP is computed by a match of the address received in the last valid shadow protocol against that at the address inputs (A9–A0) as well as against the three dedicated addresses that are internal to the ASP (DSA, RSA, and TSA). The address map is shown in Table 2.

| ADDRESS NAME                       | BINARY<br>CODE                | HEX<br>CODE | SHADOW-PROTOCOL<br>RESULT | RESULTANT<br>PRIMARY-TO-SECONDARY<br>CONNECT STATUS |

|------------------------------------|-------------------------------|-------------|---------------------------|-----------------------------------------------------|

| Reset Address (RSA)                | ess (RSA) 000000000 000 RESET |             | RESET                     |                                                     |

| Matching Address                   | A9–A0                         | A9–A0       | MATCH                     | ON                                                  |

| Disconnect Address (DSA)           | 1111111110                    | 3FE         | DISCONNECT                | OFF                                                 |

| Test Synchronization Address (TSA) | 1111111111                    | 3FF         | TEST SYNCHRONIZATION      | MULTICAST                                           |

| All Other Addresses                | All others                    | All others  | NO MATCH                  | OFF                                                 |

### Table 2. Address Map

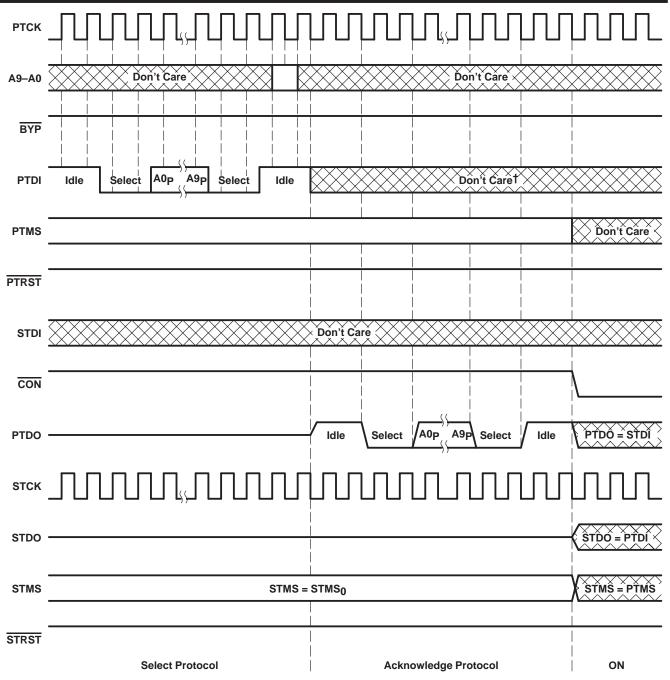

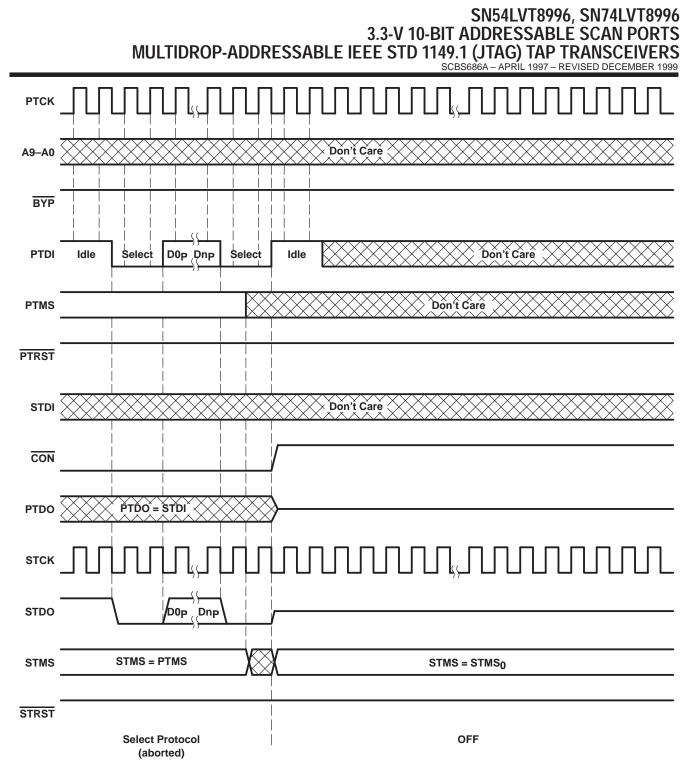

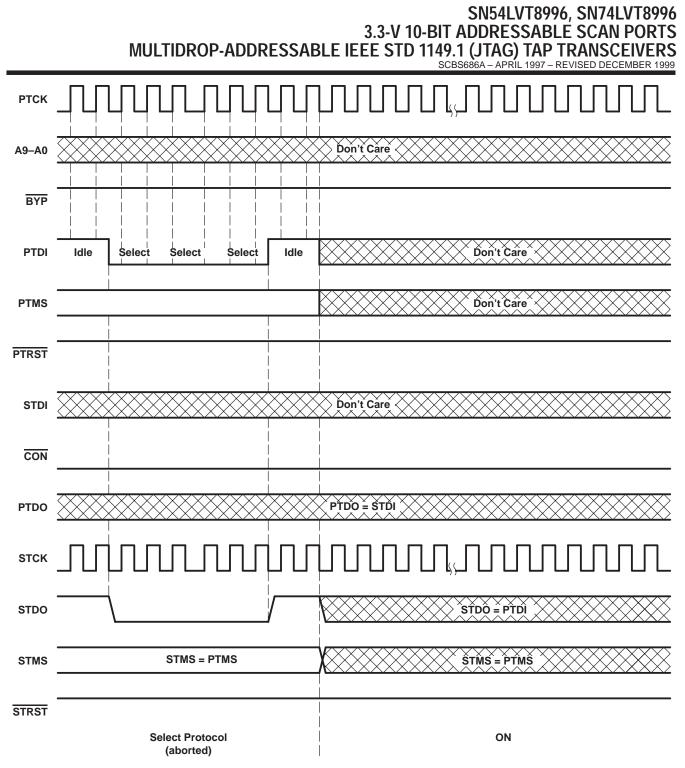

If the shadow-protocol address matches the address inputs (A9–A0), then the ASP responds by transmitting an acknowledge protocol. Following the complete transmission of the acknowledge protocol, the ASP assumes ON status (in which PTDI, PTDO, and PTMS are connected to STDO, STDI, and STMS, respectively). The ON status allows the scan chain associated with the ASP's secondary TAP to be controlled from the multidrop primary TAP as if it were directly wired as such. Figures 6 and 7 show the shadow-protocol timing for MATCH result when the prior ASP connect status is ON and OFF, respectively.

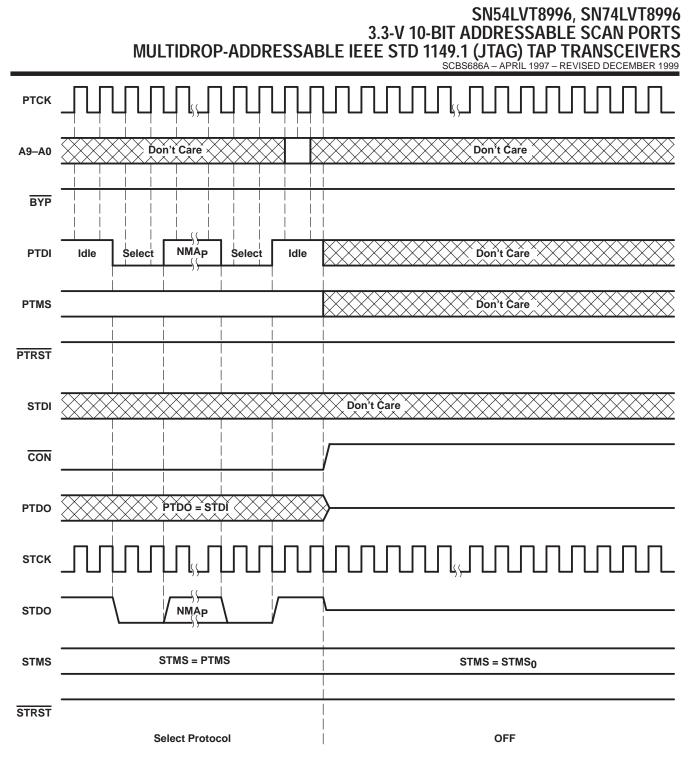

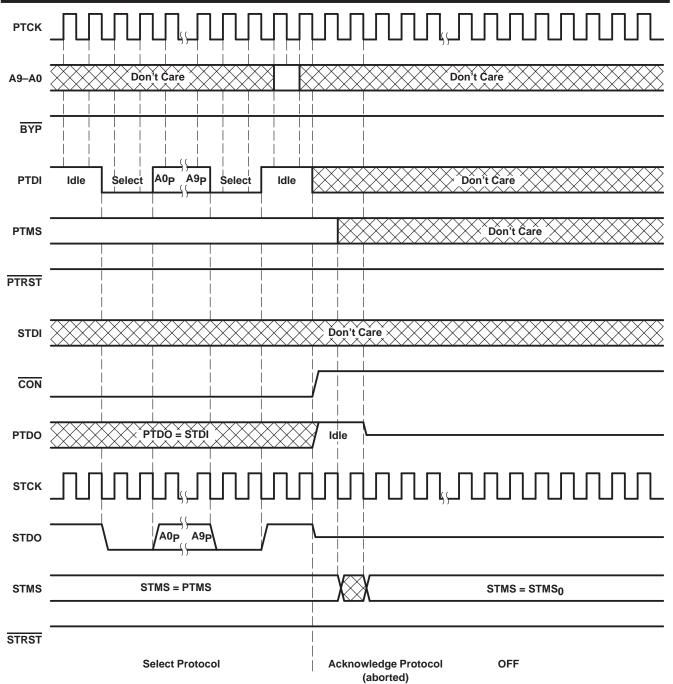

If the shadow-protocol address does not match the address inputs (A9–A0), then (unless the address is one of the three dedicated global addresses described below) the ASP responds immediately by assuming the OFF status (in which PTDO and STDO are high impedance and STMS is held at its last level). This has the effect of deselecting the scan chain associated with the ASP secondary TAP, but leaves the TAP state of the scan chain unchanged. No acknowledge protocol is sent. Figures 8 and 9 show the shadow-protocol timing for NO MATCH result when the prior ASP connect status is ON and OFF, respectively.

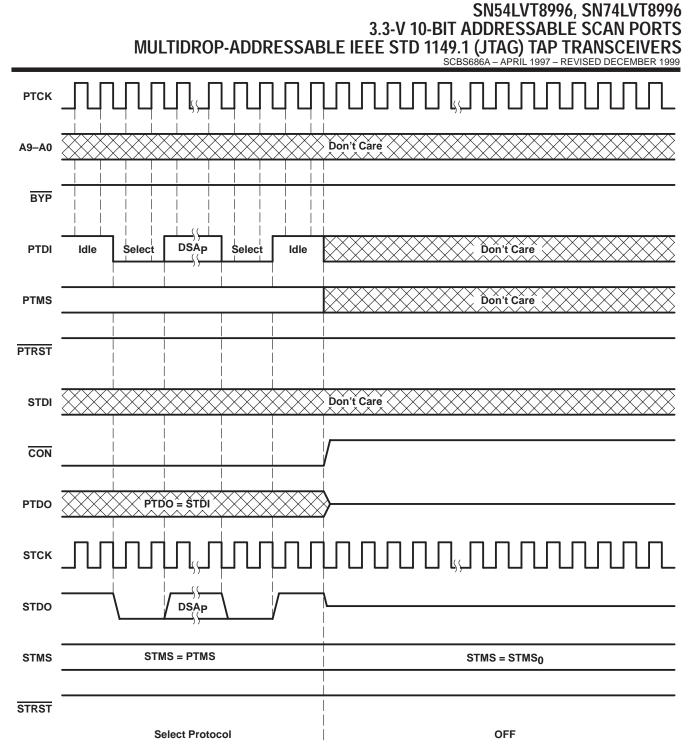

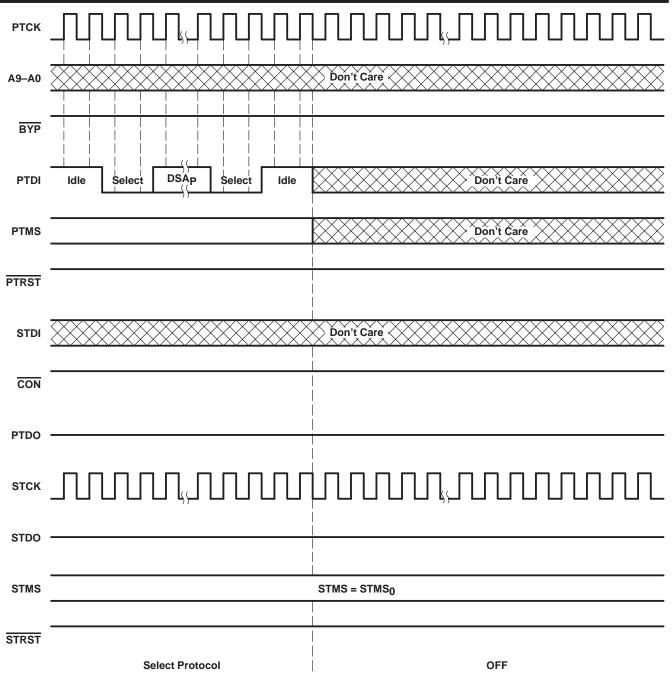

### disconnect address

The disconnect address (DSA) is one of the three internally dedicated addresses that are recognized globally. When an ASP receives the DSA, it immediately responds by assuming the OFF status (in which PTDO and STDO are high impedance and STMS is held at its last level). This has the effect of deselecting the scan chain associated with the ASP secondary TAP, but leaves the TAP state of the scan chain unchanged. No acknowledge protocol is sent. Figures 10 and 11 show the shadow-protocol timing for DISCONNECT result when the prior ASP connect status is ON and OFF, respectively.

The same result occurs when a nonmatching address is received. No specific action to disconnect an ASP is required, as a given ASP is disconnected by the address that connects another. The dedicated DSA ensures that at least one address is available for the purpose of disconnecting all receiving ASPs. It is especially useful when the currently selected scan chain is in a different TAP state than that to be selected. In such a case, the DSA is used to leave the former scan chain in the proper state, after which the primary TAP state is moved to that needed to select the latter scan chain.

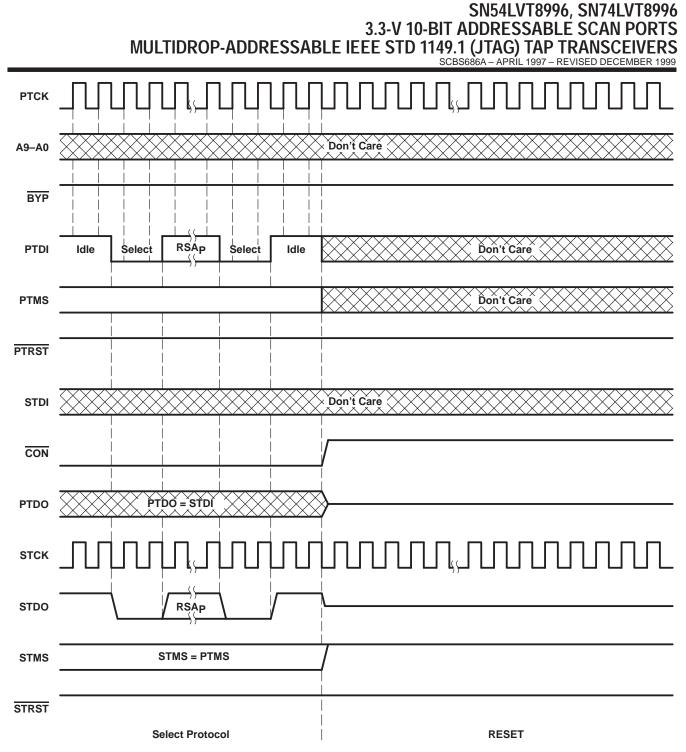

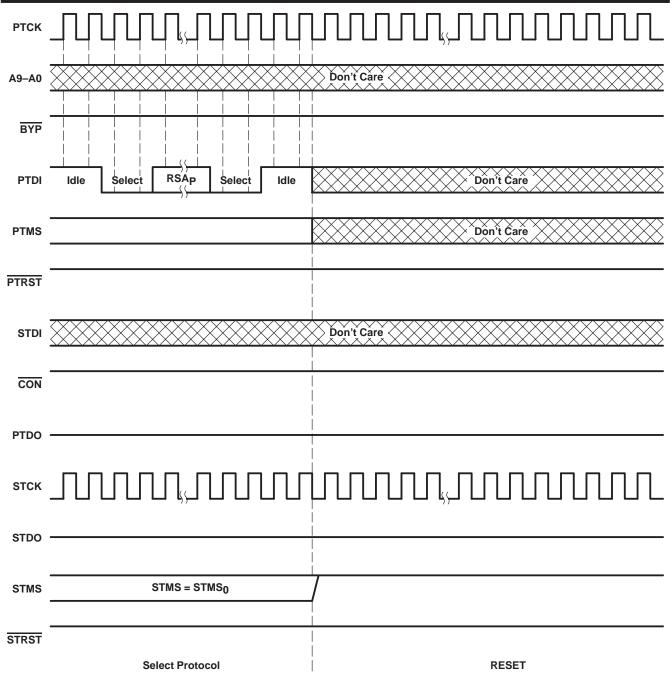

#### reset address

The reset address (RSA) is one of the three internally dedicated addresses that are recognized globally. When an ASP receives the RSA, it immediately responds by assuming the RESET status (in which PTDO and STDO are high impedance and STMS is forced to the high level). This has the effect of deselecting and resetting (to Test-Logic-Reset state) the scan chain associated with the ASP secondary TAP. No acknowledge protocol is sent. Figures 12 and 13 show the shadow-protocol timing for RESET result when the prior ASP connect status is ON and OFF, respectively.

## SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCB5686A – APRIL 1997 – REVISED DECEMBER 1999

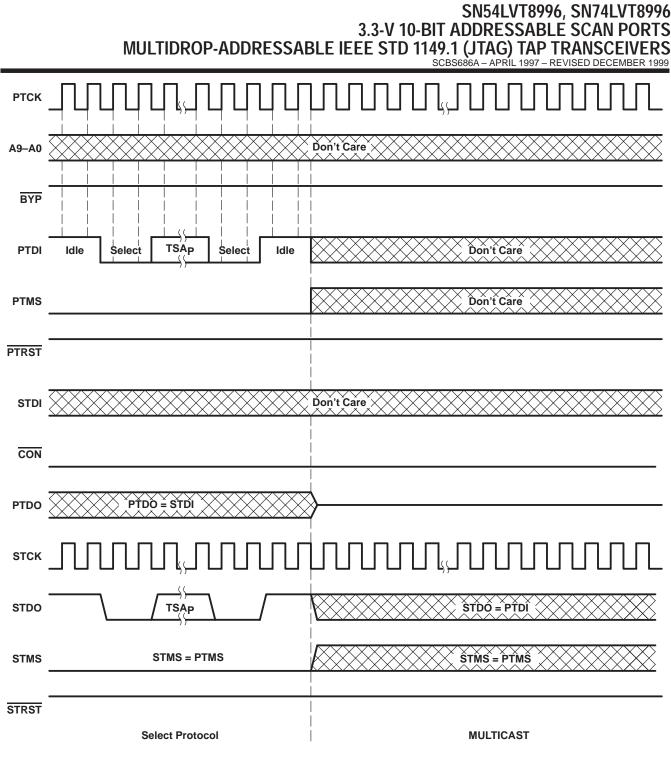

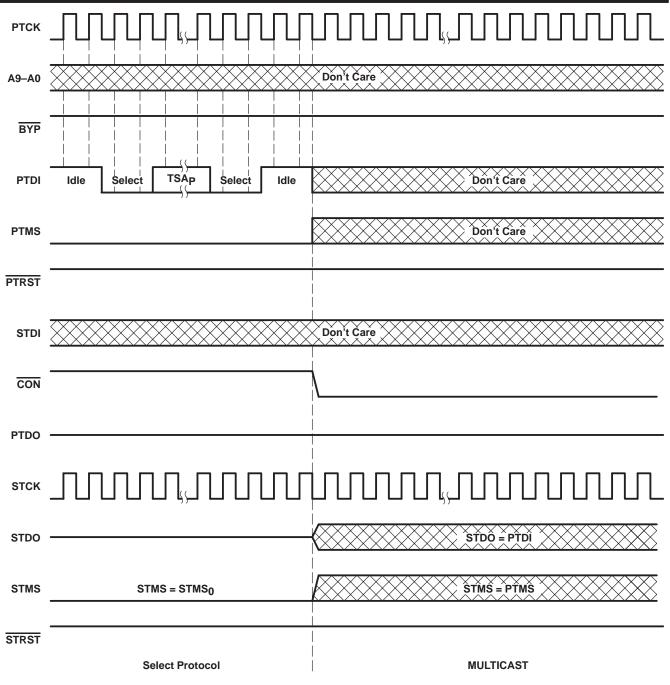

test synchronization address

The test synchronization address (TSA) is one of the three internally dedicated addresses that are recognized globally. When an ASP receives the TSA while its secondary TAP state is Pause-DR or Pause-IR, it immediately responds by assuming the MULTICAST status (in which PTDI and PTMS are connected to STDO and STMS respectively, while PTDO is high impedance). No acknowledge protocol is sent. The TSA is valid only when the TAP state of both primary and secondary is Pause-DR or Pause-IR. If the TSA is received when the TAP state of either primary or secondary is Test-Logic-Reset or Run-Test-Idle, the shadow-protocol result is considered to be DISCONNECT. Figures 14 and 15 show the shadow-protocol timing for TEST SYNCHRONIZATION result when the prior ASP connect status is ON and OFF, respectively.

The TSA allows simultaneous operation of the scan chains of all selected ASPs, either for global TAP-state movement or for scan input of common serial test data via PTDI. This is especially useful in the former case, to simultaneously move such scan chains into the Run-Test/Idle state in which module-level or module-to-module BIST operations can operate synchronous to TCK in that TAP state, and in the later case, to scan common test setup/data into multiple like modules.

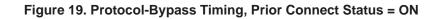

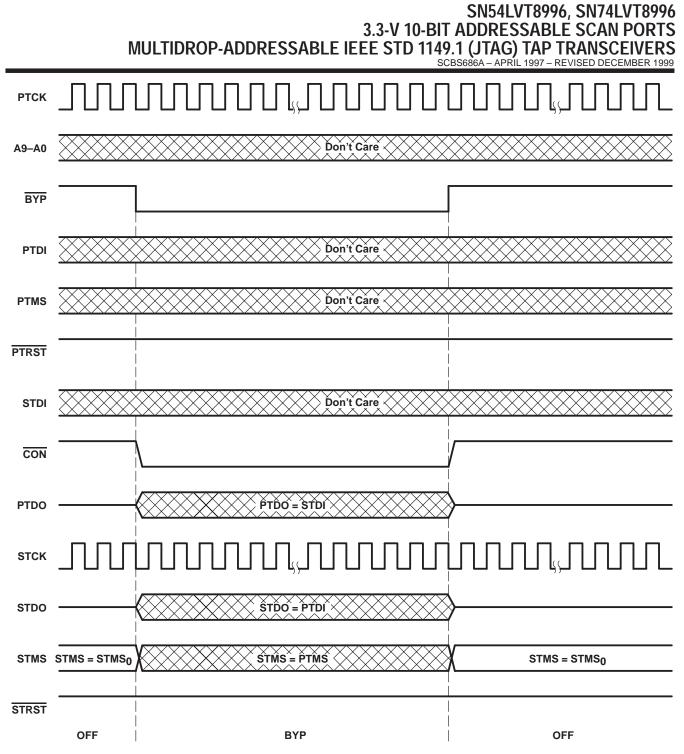

### protocol bypass

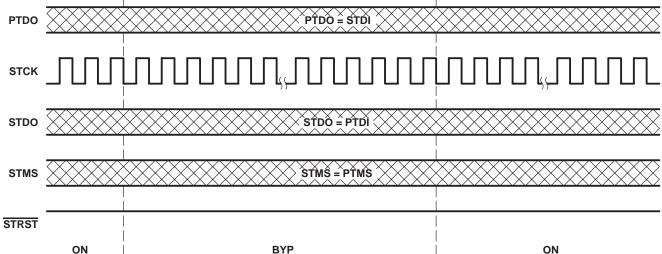

Protocol bypass is selected by a low BYP input. This protocol-bypass mode forces the ASP into BYP status (primary TAP signals are connected to secondary TAP signals) regardless of previous shadow-protocol results. The CON output is made active (low). Receipt of shadow protocols is disabled.

When BYP is taken low, the primary TAP serial data signals (PTDI, PTDO) are immediately (asynchronously to PTCK) connected to their respective secondary TAP signals (STDO, STDI). The primary TAP mode-select signal (PTMS) is also connected to its respective secondary TAP signal (STMS) unless PTRST is low, in which case STMS remains high until PTRST is released. Also, the shadow-protocol-receive block is reset to its power-up state and is held in this state such that select protocols appearing at the primary TAP are ignored.

When the BYP input is released (taken high), the ASP immediately (asynchronously to PTCK) resumes the connect status selected by the last valid shadow protocol. The shadow-protocol-receive block is again enabled to respond to select protocols.

Figures 19 and 20 show protocol-bypass timing when the ASP connect status before BYP active is ON and OFF, respectively.

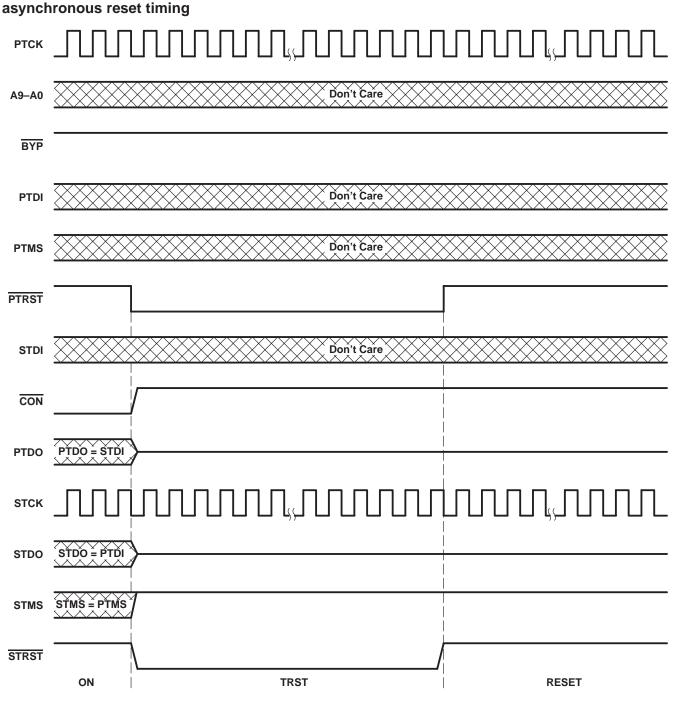

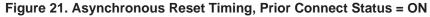

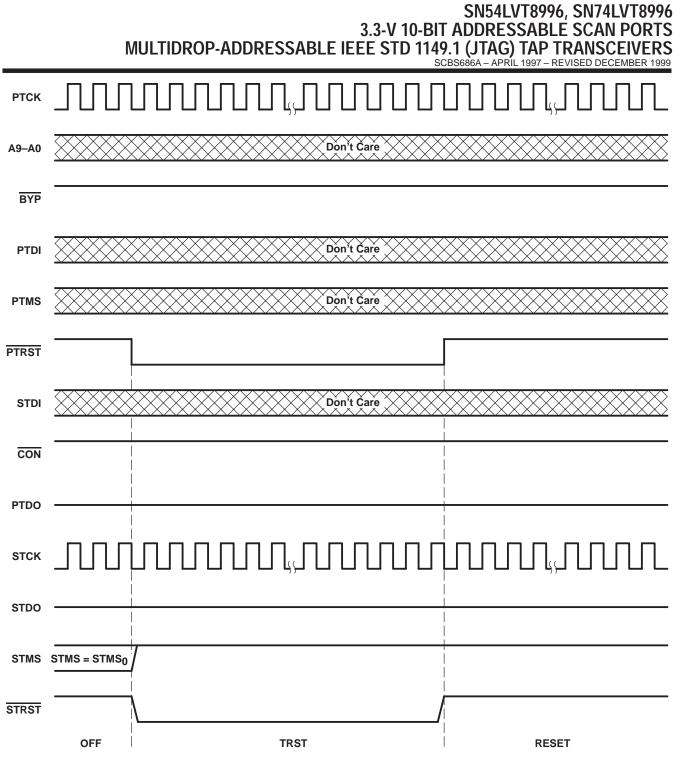

### asynchronous reset

While the PTRST input is always buffered directly to the STRST output, it also serves as an asynchronous reset for the ASP. Given that BYP is high, when PTRST goes low, the ASP immediately assumes TRST status, in which CON is high and PTDO and STDO are at high impedance. Otherwise, if BYP is low, the ASP assumes BYP/TRST status. In either case, STMS is set high so that connected IEEE Std 1149.1-compliant devices can be synchronously driven to their Test-Logic-Reset states. While PTRST is low, receipt of shadow protocols is disabled.

Figures 21 and 22 show asynchronous reset timing when the ASP connect status before PTRST active is ON and OFF, respectively. Figure 23 shows asynchronous reset timing when BYP is low.

### connect indicator

The CON output indicates secondary-scan-port activity (STDO, STMS active) regardless of whether such activity is achieved via protocol bypass or shadow protocol. If the BYP input is low, the CON output is low. Otherwise, if the BYP input is high, the CON output is low if the result of the last valid shadow protocol is MATCH or TEST SYNCHRONIZATION. In all other cases, and while acknowledge protocol is in progress, the CON output is high.

# SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCB5686A – APRIL 1997 – REVISED DECEMBER 1999

<sup>†</sup> The instantaneous value of PTDI during protocol acknowledge is "don't care" as long as the cumulative effect does not represent another valid select protocol or produce protocol result HARD ERROR.

Figure 6. Shadow-Protocol Timing, Protocol Result = MATCH, Prior Connect Status = ON

SCBS686A - APRIL 1997 - REVISED DECEMBER 1999

<sup>+</sup> The instantaneous value of PTDI during protocol acknowledge is "don't care" as long as the cumulative effect does not represent another valid select protocol or produce protocol result HARD ERROR.

Figure 7. Shadow-Protocol Timing, Protocol Result = MATCH, Prior Connect Status = OFF

Figure 8. Shadow-Protocol Timing, Protocol Result = NO MATCH, Prior Connect Status = ON

# SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCBS686A - APRIL 1997 - REVISED DECEMBER 1999

| РТСК        |                              |                          |

|-------------|------------------------------|--------------------------|

| A9–A0       | Don't Care                   | Don't Care               |

| BYP         |                              |                          |

| PTDI        | Idle Select NMAP Select Idle | Don't Care               |

| PTMS        |                              | Don't Care               |

| PTRST       |                              | <br> <br>                |

| STDI        |                              | Don't Care               |

| CON         |                              |                          |

| PTDO        |                              |                          |

| <b>STCK</b> |                              |                          |

| STDO        |                              |                          |

| STMS        |                              | STMS = STMS <sub>0</sub> |

|             |                              |                          |

| STRST       | Select Protocol              | OFF                      |

Figure 9. Shadow-Protocol Timing, Protocol Result = NO MATCH, Prior Connect Status = OFF

Figure 10. Shadow-Protocol Timing, Protocol Result = DISCONNECT, Prior Connect Status = ON

SCBS686A – APRIL 1997 – REVISED DECEMBER 1999

Figure 11. Shadow-Protocol Timing, Protocol Result = DISCONNECT, Prior Connect Status = OFF

Figure 12. Shadow-Protocol Timing, Protocol Result = RESET, Prior Connect Status = ON

SCBS686A – APRIL 1997 – REVISED DECEMBER 1999

Figure 13. Shadow-Protocol Timing, Protocol Result = RESET, Prior Connect Status = OFF

Figure 14. Shadow-Protocol Timing, Protocol Result = TEST SYNCHRONIZATION, Prior Connect Status = ON

SCBS686A – APRIL 1997 – REVISED DECEMBER 1999

Figure 15. Shadow-Protocol Timing, Protocol Result = TEST SYNCHRONIZATION, Prior Connect Status = OFF

NOTE A: The position of PTMS shown in this figure is only one of many that would produce protocol result HARD ERROR.

Figure 16. Shadow-Protocol Timing, Protocol Result = HARD ERROR (PTMS Change During Select Protocol), Prior Connect Status = ON

SCBS686A – APRIL 1997 – REVISED DECEMBER 1999

NOTE A: The position of PTMS shown in this figure is only one of many that would produce protocol result HARD ERROR.

### Figure 17. Shadow-Protocol Timing, Protocol Result = HARD ERROR (PTMS Change During Acknowledge Protocol), Prior Connect Status = ON

NOTE A: The sequence of PTDI bits shown in this figure is only one of many that would produce protocol result SOFT ERROR.

Figure 18. Shadow-Protocol Timing, Protocol Result = SOFT ERROR, Prior Connect Status = ON

SCBS686A – APRIL 1997 – REVISED DECEMBER 1999

# protocol-bypass timing РТСК A9-A0 Don'ť Care BYP PTDI Don'ť Care Ďon'ť Caré PTMS PTRST Don't Care STDI CON

$| \square$

SCBS686A – APRIL 1997 – REVISED DECEMBER 1999

SCBS686A – APRIL 1997 – REVISED DECEMBER 1999

SCBS686A - APRIL 1997 - REVISED DECEMBER 1999

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub><br>Input voltage range, V <sub>I</sub> (see Note 1) |               |

|-------------------------------------------------------------------------------------------|---------------|

| Voltage range applied to any output in the high-impedance or power-off state, $V_O$       |               |

| (see Note 1)                                                                              | –0.5 V to 7 V |

| Current into any output in the low state, IO: SN54LVT8996                                 | 96 mA         |

| SN74LVT8996                                                                               | 128 mA        |

| Current into any output in the high state, I <sub>O</sub> (see Note 2): SN54LVT8996       | 48 mA         |

| SN74LVT8996                                                                               | 64 mA         |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0)                                 |               |

| Output clamp current, $I_{OK}$ (V <sub>O</sub> < 0)                                       |               |

| Package thermal impedance, $\theta_{JA}$ (see Note 3): DW package                         |               |

| PW package                                                                                |               |

| Storage temperature range, T <sub>stg</sub>                                               |               |

|                                                                                           |               |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings can be exceeded if the input and output clamp-current ratings are observed.

- 2. This current flows only when the output is in the high state and  $V_O > V_{CC}$ .

- 3. The package thermal impedance is calculated in accordance with JESD 51.

### recommended operating conditions

|                     |                                    | SN54LVT8996  |     | SN74LV | UNIT |      |

|---------------------|------------------------------------|--------------|-----|--------|------|------|

|                     |                                    | MIN          | MAX | MIN    | MAX  | UNIT |

| VCC                 | Supply voltage                     | 2.7          | 3.6 | 2.7    | 3.6  | V    |

| VIH                 | High-level input voltage           | 2            | Ŋ   | 2      |      | V    |

| VIL                 | Low-level input voltage            |              | 0.8 |        | 0.8  | V    |

| VI                  | Input voltage                      |              | 5.5 |        | 5.5  | V    |

| ЮН                  | High-level output current          | 1            | -24 |        | -32  | mA   |

| IOL                 | Low-level output current           | 200          | 48  |        | 64   | mA   |

| Δt/Δv               | Input transition rise or fall rate | 201          | 10  |        | 10   | ns/V |

| Δt/ΔV <sub>CC</sub> | Power-up ramp rate                 | <b>Q</b> 200 |     | 200    |      | μs/V |

| TA                  | Operating free-air temperature     | -55          | 125 | -40    | 85   | °C   |

# SN54LVT8996, SN74LVT8996 **3.3-V 10-BIT ADDRESSABLE SCAN PORTS** MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCBS686A – APRIL 1997 – REVISED DECEMBER 1999

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                  |                                       | терт                                                                              | CONDITIONS                                              | SN54                 | 4LVT8996         | 6     | SN74                 | LVT8996                                                                                    | 6    | UNIT   |

|------------------|---------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------|----------------------|------------------|-------|----------------------|--------------------------------------------------------------------------------------------|------|--------|

|                  | PARAMETER                             | TEST CONDITIONS                                                                   |                                                         | MIN                  | TYP <sup>†</sup> | MAX   | MIN                  | TYP <sup>†</sup>                                                                           | MAX  | UNIT   |

| VIK              | $V_{\rm IK}$ V <sub>CC</sub> = 2.7 V, |                                                                                   | lj = -18 mA                                             |                      |                  | -1.2  |                      |                                                                                            | -1.2 | V      |

|                  |                                       | $V_{CC} = 2.7 V \text{ to } 3$                                                    | 3.6 V, I <sub>OH</sub> = −100 μA                        | V <sub>CC</sub> -0.2 |                  |       | V <sub>CC</sub> -0.2 | -1.2<br>2.4<br>2<br>0.2<br>0.2<br>0.5<br>0.4<br>0.5<br>0.5<br>10<br>±1<br>1<br>1<br>-8 -30 |      |        |

| Vari             |                                       | V <sub>CC</sub> = 2.7 V,                                                          | IOH = -8 mA                                             | 2.4                  |                  |       | 2.4                  |                                                                                            |      | V      |

| VOH              |                                       | V <sub>CC</sub> = 3 V                                                             | I <sub>OH</sub> = -24 mA                                | 2                    |                  |       |                      |                                                                                            |      | v      |

|                  |                                       | vCC = 3 v                                                                         | I <sub>OH</sub> = -32 mA                                |                      |                  |       | 2                    |                                                                                            |      |        |

|                  |                                       | V <sub>CC</sub> = 2.7 V                                                           | I <sub>OL</sub> = 100 μA                                |                      |                  | 0.2   |                      |                                                                                            | 0.2  |        |

|                  |                                       | VCC = 2.7 V                                                                       | I <sub>OL</sub> = 24 mA                                 |                      |                  | 0.5   |                      |                                                                                            | 0.5  |        |

| Voi              |                                       |                                                                                   | I <sub>OL</sub> = 16 mA                                 |                      |                  | 0.4   |                      |                                                                                            | 0.4  | V      |

| VOL              |                                       | V <sub>CC</sub> = 3 V                                                             | I <sub>OL</sub> = 32 mA                                 |                      |                  | 0.5   |                      |                                                                                            | 0.5  | v      |

|                  |                                       | VCC = 3 V                                                                         | I <sub>OL</sub> = 48 mA                                 |                      |                  | 0.55  |                      |                                                                                            |      |        |

|                  |                                       |                                                                                   | I <sub>OL</sub> = 64 mA                                 |                      |                  |       |                      |                                                                                            | 0.55 |        |

| l.               |                                       | $V_{CC} = 0 \text{ or } 3.6$                                                      | /, VI = 5.5 V                                           |                      |                  | 10    |                      |                                                                                            | 10   | μA     |

| ŧ                | PTCK                                  | V <sub>CC</sub> = 3.6 V,                                                          | $V_I = V_{CC} \text{ or } GND$                          |                      |                  | ±1    |                      |                                                                                            | ±1   | μА     |

|                  | PTDI, PTMS, PTRST                     | V <sub>CC</sub> = 3.6 V,                                                          |                                                         |                      |                  | 1     |                      |                                                                                            | 1    | ۸      |

| ΙΗ               | A9–A0, BYP, STDI                      | VCC = 3.6 V,                                                                      | $V_{I} = V_{CC}$                                        |                      | Ela              | 1     |                      |                                                                                            | 1    | μA     |

| lu.              | PTDI, PTMS, PTRST                     |                                                                                   | VI = GND                                                | -8                   | EL               | -30   | -8                   |                                                                                            | -30  | ۸      |

| ۱Ľ               | A9–A0, BYP, STDI                      | V <sub>CC</sub> = 3.6 V,                                                          | V] = GND                                                | -25                  | 4                | -100  | -25                  | 830<br>25100<br>±100                                                                       | -100 | μA     |

| loff             |                                       | $V_{CC} = 0,$                                                                     | $V_{I} \text{ or } V_{O} = 0 \text{ to } 4.5 \text{ V}$ |                      | ŝ                |       |                      |                                                                                            | ±100 | μA     |

| IOZH             | PTDO, STDO                            | V <sub>CC</sub> = 3.6 V,                                                          | V <sub>O</sub> = 3 V                                    | 2                    | 3                | 5     |                      |                                                                                            | 5    | μΑ     |

| I <sub>OZL</sub> | PTDO, STDO                            | V <sub>CC</sub> = 3.6 V,                                                          | V <sub>O</sub> = 0.5 V                                  | R                    |                  | -5    |                      |                                                                                            | -5   | μΑ     |

| IOZPU            | J                                     | $V_{CC} = 0$ to 1.5 \                                                             | /, $V_{O} = 0.5 V$ to 3 V,                              |                      |                  | ±100* |                      |                                                                                            | ±100 | μΑ     |

| IOZPD            | )                                     | $V_{CC} = 1.5 V to 0$                                                             | 0, $V_{O} = 0.5 V$ to 3 V                               |                      |                  | ±100* |                      |                                                                                            | ±100 | μA     |

|                  |                                       |                                                                                   | OFF, STCK = H,<br>STMS = H                              |                      |                  | 2     |                      |                                                                                            | 2    |        |

| Icc              |                                       | V <sub>CC</sub> = 3.6 V,<br>V <sub>I</sub> = V <sub>CC</sub> or                   | ON, PTDO = L,<br>STCK = L,<br>STDO = L, STMS = L        |                      |                  | 20    |                      |                                                                                            | 20   | mA     |

|                  |                                       | GND,<br>I <sub>O</sub> = 0                                                        | ON, PTDO = H,<br>STCK = H,<br>STDO = H,<br>STMS = H     |                      |                  | 7     |                      |                                                                                            | 7    | iii) ( |

|                  |                                       |                                                                                   | TRST, STCK = L                                          |                      |                  | 10    |                      |                                                                                            | 10   |        |

| ∆ICC‡            |                                       | $V_{CC} = 3 V \text{ to } 3.6$<br>One input at $V_{C}$<br>Other inputs at $V_{C}$ | с — 0.6 V,                                              |                      |                  | 0.2   |                      |                                                                                            | 0.2  | mA     |

| Ci               |                                       | $V_{I} = 3 V \text{ or } 0$                                                       |                                                         |                      | 3.5              |       |                      | 3.5                                                                                        |      | pF     |

| Co               |                                       | $V_0 = 3 V \text{ or } 0$                                                         |                                                         |                      | 6.5              |       |                      | 6.5                                                                                        |      | pF     |

\* On products compliant to MIL-PRF-38535, this parameter is not production tested.

<sup>†</sup> All typical values are at  $V_{CC}$  = 3.3 V,  $T_A$  = 25°C. <sup>‡</sup> This is the increase in supply current for each input that is at the specified TTL voltage level rather than  $V_{CC}$  or GND.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

# SN54LVT8996, SN74LVT8996 3.3-V 10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 (JTAG) TAP TRANSCEIVERS SCB5686A – APRIL 1997 – REVISED DECEMBER 1999

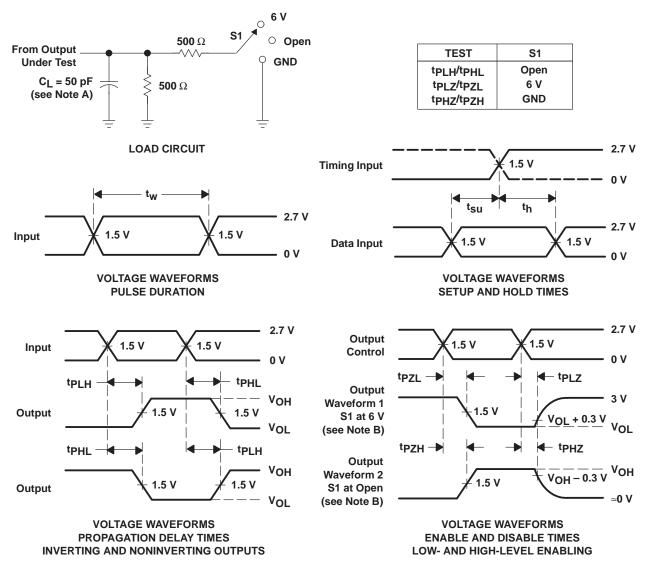

### timing requirements over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Figure 24)

|                                    |                               |                              |                                           | SN54LV      | T8996 | SN74LV | T8996 | UNIT |

|------------------------------------|-------------------------------|------------------------------|-------------------------------------------|-------------|-------|--------|-------|------|

|                                    |                               | -                            |                                           | MIN         | MAX   | MIN    | MAX   | UNIT |

| f                                  | Clock frequency               | РТСК                         | V <sub>CC</sub> = 2.7 V                   |             | 20    |        | 20    | MHz  |

| f <sub>clock</sub> Clock frequency | Clock nequency                | FICK                         | $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{V}$ |             | 25    |        | 25    |      |

|                                    |                               | BYP low                      | t                                         | 8           |       | 8      |       |      |

|                                    | Pulse duration                | PTCK hig                     | gh                                        | 20          | M     | 20     |       | ns   |

| ١W                                 | t <sub>w</sub> Pulse duration | PTCK low                     |                                           | 12          | ľ.    | 12     |       | 115  |

|                                    |                               | PTRST low                    |                                           |             | 2     | 9      |       |      |

|                                    |                               | A9–A0 before PTCK↓‡          |                                           | 10.2        |       | 10.2   |       |      |

|                                    | Satur time                    | PTDI bef                     | ore PTCK↑                                 | 10.1        |       | 10.1   |       | ns   |

| t <sub>su</sub>                    | Setup time                    | PTMS be                      | efore BYP↑†                               | <b>0</b> 4  |       | 4      |       | 115  |

|                                    |                               | PTMS be                      | efore PTCK↑                               | <b>२</b> 10 |       | 10     |       |      |

|                                    |                               | A9–A0 at                     | fter PTCK↓‡                               | 4           |       | 4      |       |      |

|                                    | Hold time                     | PTDI after PTCK <sup>↑</sup> |                                           | 4           |       | 4      |       | ~~   |

| th                                 |                               | PTMS after BYP↑†             |                                           | 4           |       | 4      |       | ns   |

|                                    |                               | PTMS af                      | ter PTCK↑                                 | 4           |       | 4      |       |      |

<sup>†</sup> In normal application of the ASP, such timing requirements with respect to BYP are met implicitly and, therefore, need not be considered.

<sup>‡</sup> These requirements apply only in the case in which the address inputs are changed during a shadow protocol. For normal application of the ASP, it is recommended that the address inputs remain static throughout any shadow protocols. In such cases, the timing of address inputs relative to PTCK need not be considered.

SCBS686A – APRIL 1997 – REVISED DECEMBER 1999

### switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Figure 24)

|                               |                               |                |                           | SN54LVT8996  |                         |      |      |  |

|-------------------------------|-------------------------------|----------------|---------------------------|--------------|-------------------------|------|------|--|

| PARAMETER                     | FROM<br>(INPUT)               | TO<br>(OUTPUT) | V <sub>CC</sub> =<br>± 0. |              | V <sub>CC</sub> = 2.7 V |      | UNIT |  |

|                               |                               |                | MIN                       | MAX          | MIN                     | MAX  |      |  |

| fmax                          | РТСК                          |                | 25                        |              | 20                      |      | MHz  |  |

| <sup>t</sup> PLH              | BYP↑                          | CON            | 1                         | 8.7          | 1                       | 10   | ns   |  |

| <sup>t</sup> PHL              | BYP↓                          | CON            | 1                         | 10           | 1                       | 11.6 | 115  |  |

| <sup>t</sup> PLH              | BYP↓                          | STMS           | 2.5                       | 12.6         | 2.5                     | 15.4 | ns   |  |

| <sup>t</sup> PHL              | BTP↓                          | 31103          | 2.5                       | 12.1         | 2.5                     | 13.9 | 115  |  |

| <sup>t</sup> PLH              | РТСК                          | STCK           | 1                         | 10.2         | 1                       | 11.8 | ns   |  |

| <sup>t</sup> PHL              | 1 TOK                         | 5101           | 1                         | 10.5         | 1                       | 12.2 | 115  |  |

| <sup>t</sup> PLH              | РТСК↓                         | CON            | 3.5                       | 22           | 3.5                     | 26.4 | ns   |  |

| <sup>t</sup> PHL              |                               | CON            | 3.5                       | 24.6         | 3.5                     | 28.8 | 115  |  |

| <sup>t</sup> PLH              | PTCK↓                         | PTDO           | 3                         | 15.5         | 3                       | 18.3 | ns   |  |

| <sup>t</sup> PHL              | (shadow-protocol acknowledge) | 1100           | 3                         | 15.7         | 3                       | 18.4 | 113  |  |

| t <sub>PLH</sub> †            | PTCK↓                         | STMS           | 5.5                       | 20.1         | 5.5                     | 25.1 | ns   |  |

| <sup>t</sup> PHL <sup>†</sup> | (connect)                     | 61116          | 5.5                       | 20.3         | 5.5                     | 24.2 | 113  |  |

| <sup>t</sup> PLH              | PTDI                          | STDO           | 1                         | <b>Q</b> 8.8 | 1                       | 10.3 | ns   |  |

| <sup>t</sup> PHL              |                               | 3100           | 1                         | 9            | 1                       | 10.6 | 115  |  |