# Contents

| Page | Section   | Title                                  |  |  |

|------|-----------|----------------------------------------|--|--|

| 5    | 1.        | Introduction                           |  |  |

| 5    | 1.1.      | System Architecture                    |  |  |

| 7    | 2.        | Functional Description                 |  |  |

| 7    | 2.1.      | Analog Front-End                       |  |  |

| 7    | 2.1.1.    | Input Selector                         |  |  |

| 7    | 2.1.2.    | Clamping                               |  |  |

| 7    | 2.1.3.    | Automatic Gain Control                 |  |  |

| 7    | 2.1.4.    | Analog-to-Digital Converters           |  |  |

| 7    | 2.1.5.    | ADC Range                              |  |  |

| 7    | 2.1.6.    | Digitally Controlled Clock Oscillator  |  |  |

| 9    | 2.2.      | Color Decoder                          |  |  |

| 9    | 2.2.1.    | Demodulator                            |  |  |

| 9    | 2.2.2.    | IF-Compensation                        |  |  |

| 10   | 2.2.3.    | Chrominance Filter                     |  |  |

| 10   | 2.2.4.    | Frequency Demodulator                  |  |  |

| 10   | 2.2.5.    | Burst Detection                        |  |  |

| 11   | 2.2.6.    | Color Killer Operation                 |  |  |

| 11   | 2.2.7.    | PAL Compensation/1-H Comb Filter       |  |  |

| 12   | 2.2.8.    | Luminance Notch Filter                 |  |  |

| 12   | 2.3.      | Video Sync Processing                  |  |  |

| 13   | 2.4.      | Component Processing                   |  |  |

| 14   | 2.4.1.    | Horizontal Resizer                     |  |  |

| 15   | 2.4.2.    | Skew Correction                        |  |  |

| 16   | 2.4.3.    | Peaking and Coring                     |  |  |

| 16   | 2.4.4.    | YCbCr Color Space                      |  |  |

| 16   | 2.4.5.    | Video Adjustments                      |  |  |

| 17   | 2.5.      | Video Output Interface                 |  |  |

| 17   | 2.5.1.    | Output Formats                         |  |  |

| 17   | 2.5.1.1.  | YUV 4:2:2 with Separate Syncs/ITU-R601 |  |  |

| 18   | 2.5.1.2.  | Embedded Reference Headers/ITU-R656    |  |  |

| 20   | 2.5.1.3.  | Embedded Timing Codes (BStream)        |  |  |

| 20   | 2.5.2.    | Bus Shuffler                           |  |  |

| 20   | 2.5.3.    | Output Multiplexer                     |  |  |

| 21   | 2.5.4.    | Output Ports                           |  |  |

| 21   | 2.5.5.    | Half-Clock Mode                        |  |  |

| 22   | 2.6.      | Video Data Transfer                    |  |  |

| 24   | 2.7.      | Video Reference Signals                |  |  |

| 24   | 2.7.1.    | HREF                                   |  |  |

| 24   | 2.7.2.    | VREF                                   |  |  |

| 24   | 2.7.3.    | Odd/Even Information (FIELD)           |  |  |

| 24   | 2.7.4.    | VACT                                   |  |  |

| 26   | 2.8.      | Windowing the Video Field              |  |  |

| 27   | 2.9.      | Temporal Decimation                    |  |  |

| 28   | 2.10.     | Data Slicer                            |  |  |

| 28   | 2.10.1.   | Data Broadcast Systems                 |  |  |

| 29   | 2.10.2.   | Slicer Functions                       |  |  |

| 29   | 2.10.2.1. | Features                               |  |  |

|      |           |                                        |  |  |

# Contents, continued

| Page | Section   | Title                                               |

|------|-----------|-----------------------------------------------------|

| 29   | 2.10.2.2. | Input                                               |

| 29   | 2.10.2.3. | Automatic Adaptation                                |

| 29   | 2.10.2.4. | Standard Selection                                  |

| 30   | 2.10.2.5. | Output                                              |

| 31   | 2.11.     | VBI Data Acquisition                                |

| 31   | 2.11.1.   | Raw Teletext Data                                   |

| 32   | 2.11.2.   | Sliced VBI Data                                     |

| 33   | 2.12.     | Operational Modes                                   |

| 33   | 2.12.1.   | Open Mode                                           |

| 33   | 2.12.2.   | Forced Mode                                         |

| 33   | 2.12.3.   | Scan Mode                                           |

| 33   | 2.12.4.   | Transition Behavior                                 |

| 36   | 2.13.     | Control Interface                                   |

| 36   | 2.13.1.   | Overview                                            |

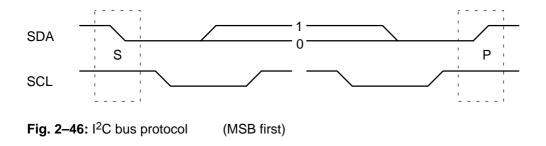

| 36   | 2.13.2.   | I <sup>2</sup> C-Bus Interface                      |

| 36   | 2.13.3.   | Reset and I <sup>2</sup> C Device Address Selection |

| 36   | 2.13.4.   | Protocol Description                                |

| 37   | 2.13.5.   | FP Control and Status Registers                     |

| 38   | 2.14.     | Initialization of the VPX                           |

| 38   | 2.14.1.   | Power on Reset                                      |

| 38   | 2.14.2.   | Software Reset                                      |

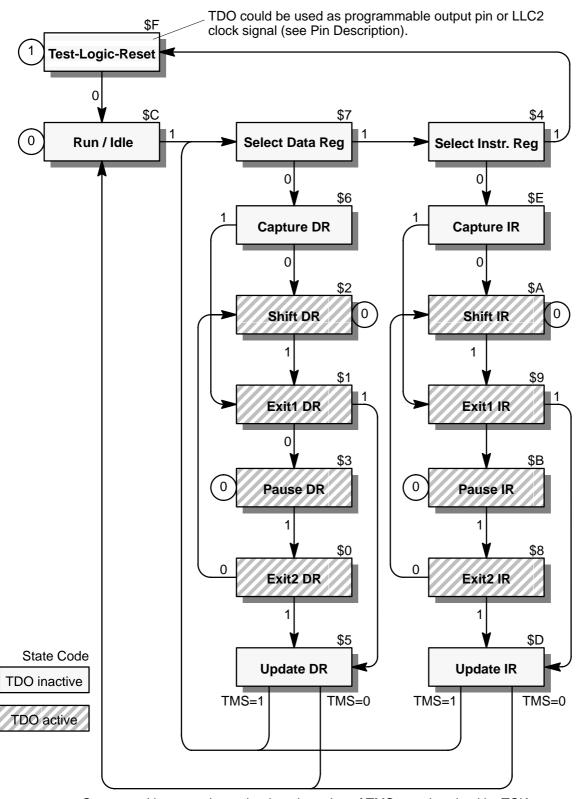

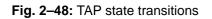

| 39   | 2.15.     | JTAG Boundary-Scan, Test Access Port (TAP)          |

| 39   | 2.15.1.   | General Description                                 |

| 39   | 2.15.2.   | TAP Architecture                                    |

| 39   | 2.15.2.1. | TAP Controller                                      |

| 39   | 2.15.2.2. | Instruction Register                                |

| 39   | 2.15.2.3. | Boundary Scan Register                              |

| 40   | 2.15.2.4. | Bypass Register                                     |

| 40   | 2.15.2.5. | Device Identification Register                      |

| 40   | 2.15.2.6. | Master Mode Data Register                           |

| 40   | 2.15.3.   | Exception to IEEE 1149.1                            |

| 40   | 2.15.4.   | IEEE 1149.1–1990 Spec Adherence                     |

| 40   | 2.15.4.1. | Instruction Register                                |

| 40   | 2.15.4.2. | Public Instructions                                 |

| 41   | 2.15.4.3. | Self-Test Operation                                 |

| 41   | 2.15.4.4. | Test Data Registers                                 |

| 41   | 2.15.4.5. | Boundary-Scan Register                              |

| 41   | 2.15.4.6. | Device Identification Register                      |

| 41   | 2.15.4.7. | Performance                                         |

| 45   | 2.16.     | Enable/Disable of Output Signals                    |

| 46   | 2.17.     | Low Power Mode                                      |

| 47   | 3.        | Specifications                                      |

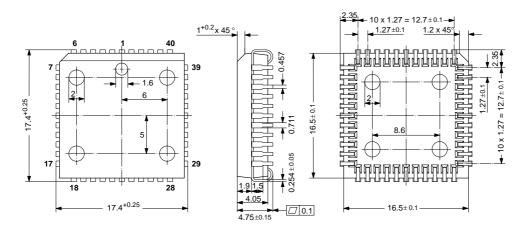

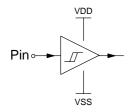

| 47   | 3.1.      | Outline Dimensions                                  |

| 51   | 3.2.      | Pin Connections and Short Descriptions              |

| 48   | 3.3.      | Pin Descriptions                                    |

| 50   | 3.4.      | Pin Configuration                                   |

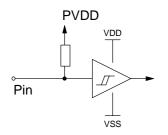

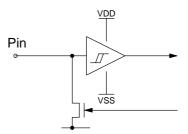

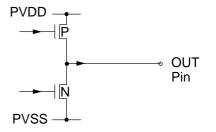

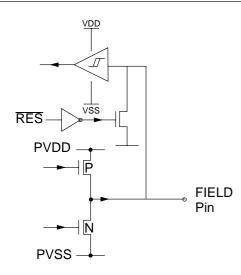

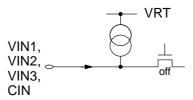

| 51   | 3.5.      | Pin Circuits                                        |

# Contents, continued

| Page | Section   | Title                                                        |

|------|-----------|--------------------------------------------------------------|

| 53   | 4.        | Electrical Characteristics                                   |

| 53   | 4.1.      | Absolute Maximum Ratings                                     |

| 54   | 4.2.      | Recommended Operating Conditions                             |

| 54   | 4.2.1.    | Recommended Analog Video Input Conditions                    |

| 55   | 4.2.2.    | Recommended I <sup>2</sup> C Conditions                      |

| 55   | 4.2.3.    | Recommended Digital Inputs Levels of RES, OE, TCK, TMS, TDI  |

| 56   | 4.2.4.    | Recommended Crystal Characteristics                          |

| 57   | 4.3.      | Characteristics                                              |

| 57   | 4.3.1.    | Current Consumption                                          |

| 57   | 4.3.2.    | Characteristics, Reset                                       |

| 57   | 4.3.3.    | XTAL Input Characteristics                                   |

| 58   | 4.3.4.    | Characteristics, Analog Front-End and ADCs                   |

| 59   | 4.3.5.    | Characteristics, Control Bus Interface                       |

| 59   | 4.3.6.    | Characteristics, JTAG Interface (Test Access Port TAP)       |

| 60   | 4.3.7.    | Characteristics, Digital Inputs/Outputs                      |

| 60   | 4.3.8.    | Digital Video Interface                                      |

| 61   | 4.3.10.   | Characteristics, TTL Output Driver                           |

| 61   | 4.3.10.1. | TTL Output Driver Type A                                     |

| 61   | 4.3.10.2. | TTL Output Driver Type B                                     |

| 63   | 5.        | Timing Diagrams                                              |

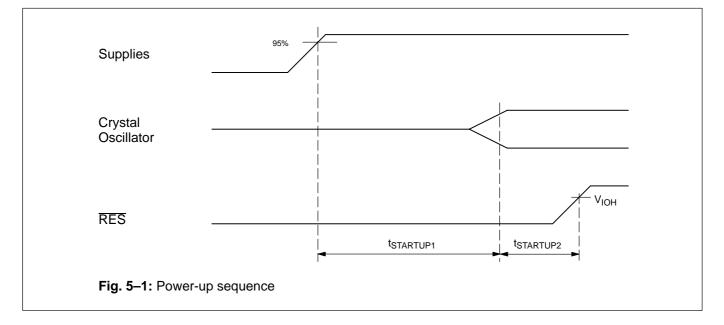

| 63   | 5.1.      | Power-up Sequence                                            |

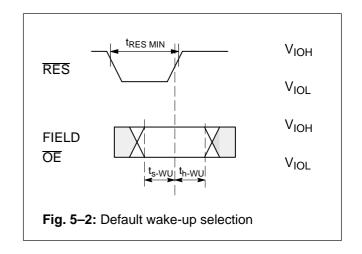

| 63   | 5.2.      | Default Wake-up Selection                                    |

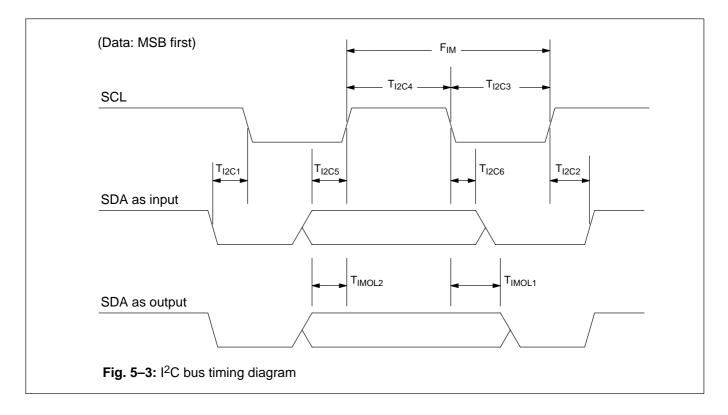

| 64   | 5.3.      | I <sup>2</sup> C Bus Timing Diagram                          |

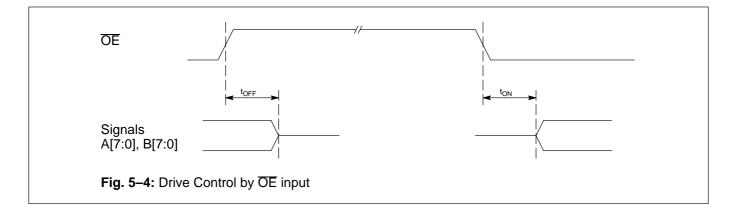

| 64   | 5.4.      | Output Enable by Pin OE                                      |

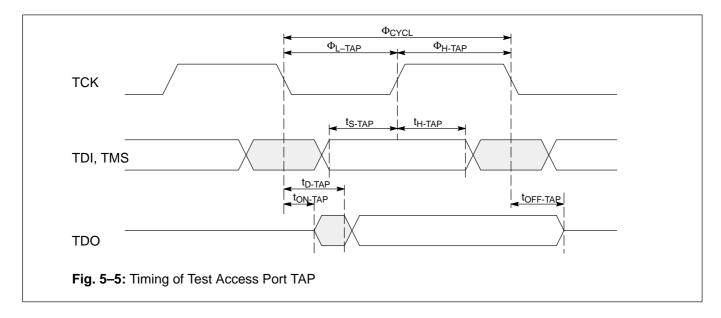

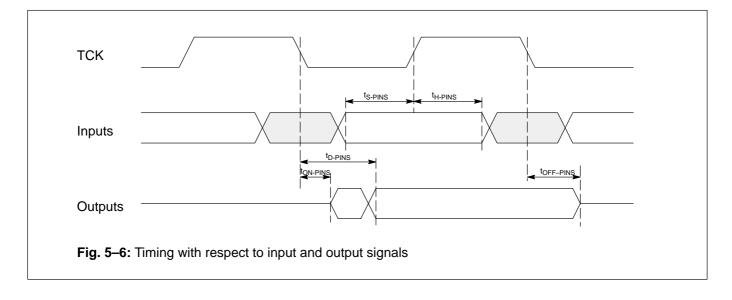

| 65   | 5.5.      | Timing of the Test Access Port TAP                           |

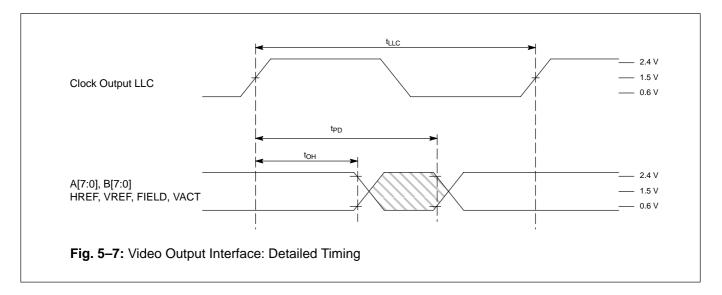

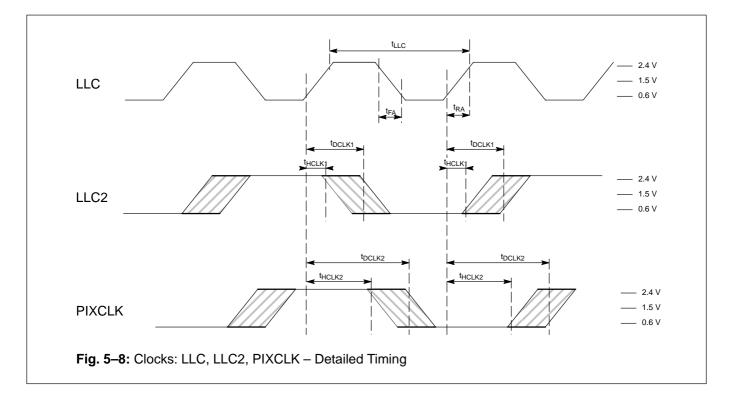

| 66   | 5.7.      | Timing Diagram of the Digital Video Interface                |

| 66   | 5.7.1.    | Characteristics, Clock Signals                               |

| 67   | 6.        | Control and Status Registers                                 |

| 68   | 6.1.      | Overview                                                     |

| 71   | 6.1.1.    | Description of I <sup>2</sup> C Control and Status Registers |

| 75   | 6.1.2.    | Description of FP Control and Status Registers               |

| 85   | 6.1.2.1.  | TV Standard Coding                                           |

| 86   | 7.        | Application Notes                                            |

| 86   | 7.1.      | Differences between VPX 3220A and VPX 322xD                  |

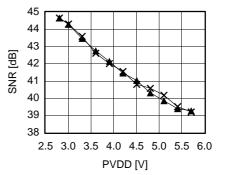

| 86   | 7.2.      | Impact to Signal to Noise Ratio                              |

| 86   | 7.3.      | Control Interface                                            |

| 86   | 7.3.1.    | Symbols                                                      |

| 86   | 7.3.2.    | Write Data into I <sup>2</sup> C Register                    |

| 86   | 7.3.3.    | Read Data from I <sup>2</sup> C Register                     |

| 86   | 7.3.4.    | Write Data into FP Register                                  |

| 86   | 7.3.5.    | Read Data from FP Register                                   |

| 87   | 7.3.6.    | Sample Control Code                                          |

| 87   | 7.4.      | Xtal Supplier                                                |

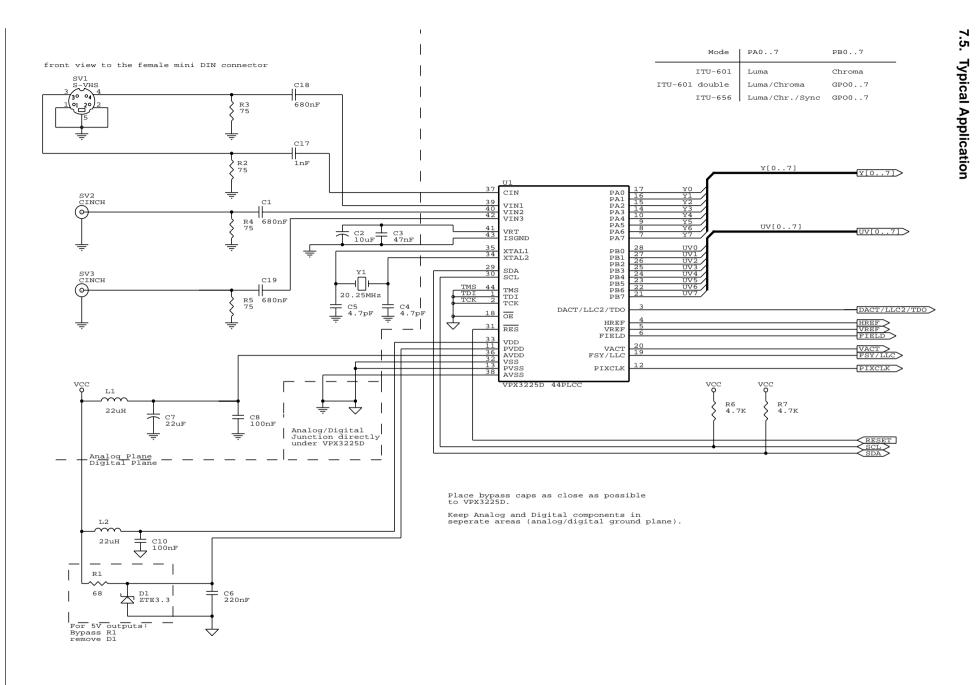

| 88   | 7.5.      | Typical Application                                          |

| 92   | 8.        | Data Sheet History                                           |

#### Video Pixel Decoder

#### Note: This data sheet describes functions and characteristics of VPX 322xD–B2.

#### 1. Introduction

The Video Pixel Decoders VPX 3225D and VPX 3224D are the second generation of full feature video acquisition ICs for consumer video and multimedia applications. All of the processing necessary to convert an analog video signal into a digital component stream have been integrated onto a single 44-pin IC. Moreover, the VPX 3225D provides text slicing for intercast, teletext, and closed caption. Both chips are pin compatible to VPX 3220A, VPX 3216B, and VPX 3214C. Notable features include:

#### **Video Decoding**

- multistandard color decoding: NTSC-M, NTSC-443

PAL-BGHI, PAL-M, PAL-N, PAL-60

SECAM

S-VHS

- NTSC with Y/C comb filter

- two 8-bit video A/D converters with clamping and automatic gain control (AGC)

- four analog inputs with integrated selector for:

3 composite video sources (CVBS), or

2 Y/C sources (S-VHS), or

- 2 composite video sources and one Y/C source.

- horizontal and vertical sync detection for all standards

## **Video Processing**

- hue, brightness, contrast, and saturation control

- dual window cropping and scaling

- horizontal resizing between 32 and 864 pixels/line

- vertical resizing by line dropping

- high quality anti-aliasing filter

- scaling controlled peaking and coring

## **Video Interfacing**

- YCbCr 4:2:2 format

- ITU-R 601 compliant output format

- ITU-R 656 compliant output format

- BStream compliant output format

- square pixel format (640 or 768 pixel/line)

- 8-bit or 16-bit synchronous output mode

- 13.5 MHz/16-bit and 27 MHz/8-bit output rate

- VBI bypass and raw ADC data output

## Text Support (VPX 3225D only)

- multistandard teletext, data slicer, intercast WST, VPS, WSS CAPTION (1x,2x), NABTS Antiope VITC

- high performance text decoding without CPU

- programmable to new standards via I<sup>2</sup>C

- automatic slice level adaptation

- PAL and NTSC mode

- VBI and full-field mode

- text data insertion into video stream

- simultaneous acquisition of teletext, VPS, WSS, and caption

#### Miscellaneous

- 44-pin PLCC packages

- total power consumption of below 1 W

- I<sup>2</sup>C serial control, 2 different device addresses

- single on-chip clock generation, only one crystal needed for all standards

- user programmable output pins

- power-down mode

- IEEE 1149.1 (JTAG) boundary scan interface

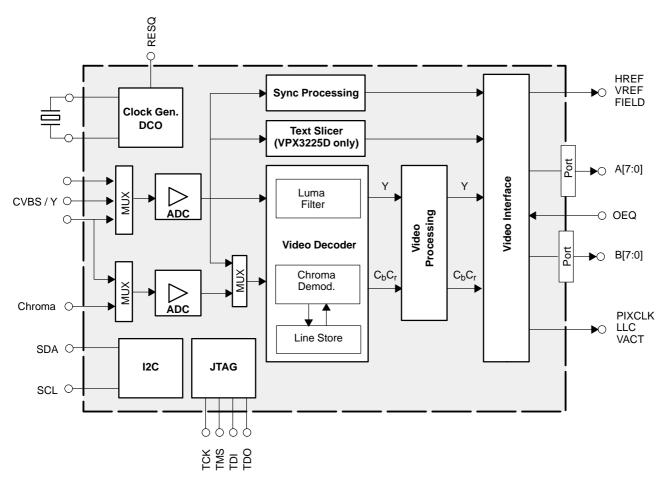

## 1.1. System Architecture

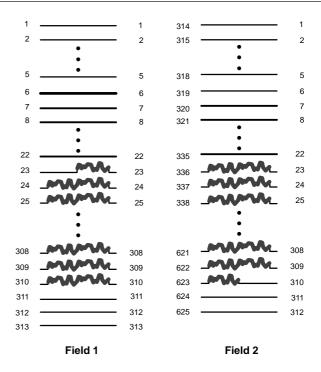

The block diagram (Fig. 1–1) illustrates the signal flow through the VPX. A sampling stage performs 8-bit A/D conversion, clamping, and AGC. The color decoder separates the luma and chroma signals, demodulates the chroma, and filters the luminance. A sync slicer detects the sync edge and computes the skew relative to the sample clock. The video processing stage resizes the YCbCr samples, adjusts the contrast and brightness, and interpolates the chroma. The text slicer extracts lines with text information and delivers decoded data bytes to the video interface.

**Note:** The VPX 3225D and VPX 3224D are not register compatible with the VPX 3220A, VPX 3216B, and VPX 3214C family.

# VPX 3225D, VPX 3224D

Fig. 1–1: Block diagram of the VPX 3224D, VPX 3225D

# 2. Functional Description

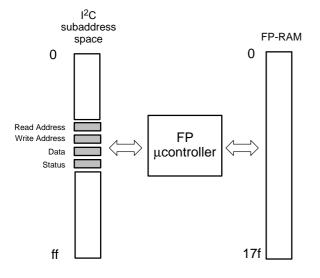

The following sections give an overview of the different functional blocks within the VPX. Most of them are controlled by the Fast Processor ('FP') embedded in the decoder. For controlling, there are two classes of registers:  $I^{2}C$  registers (directly addressable via  $I^{2}C$  bus) and FP-RAM registers (ram memory of the FP; indirectly addressable via  $I^{2}C$  bus). For further information, see section 2.13.1.

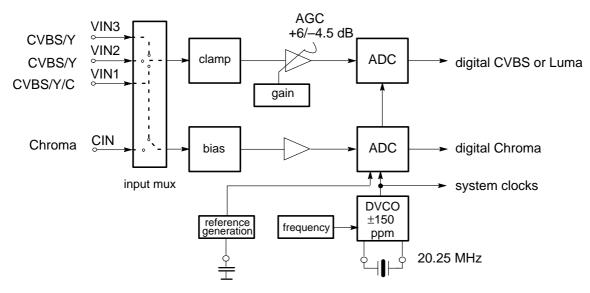

# 2.1. Analog Front-End

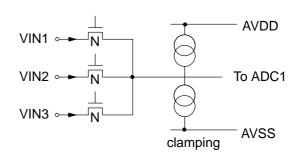

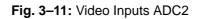

This block provides the analog interfaces to all video inputs and mainly carries out analog-to-digital conversion for the following digital video processing. A block diagram is given in Fig. 2–1.

Clamping, AGC, and clock DCO are digitally controlled. The control loops are closed by the embedded processor.

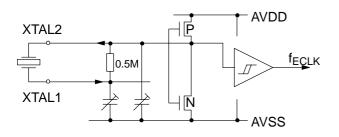

# 2.1.1. Input Selector

Up to four analog inputs can be connected. Three inputs (VIN1–3) are for input of composite video or S-VHS luma signal. These inputs are clamped to the sync back porch and are amplified by a variable gain amplifier. Two inputs, one dedicated (CIN) and one shared (VIN1), are for connection of S-VHS carrier-chrominance signal. The chrominance input is internally biased and has a fixed gain amplifier.

# 2.1.2. Clamping

The composite video input signals are AC coupled to the IC. The clamping voltage is stored on the coupling ca-

pacitors and is generated by digitally controlled current sources. The clamping level is the back porch of the video signal. S-VHS chroma is AC coupled. The input pin is internally biased to the center of the ADC input range.

# 2.1.3. Automatic Gain Control

A digitally working automatic gain control adjusts the magnitude of the selected baseband by +6/-4.5 dB in 64 logarithmic steps to the optimal range of the ADC. The gain of the video input stage including the ADC is 213 steps/V with the AGC set to 0 dB.

## 2.1.4. Analog-to-Digital Converters

Two ADCs are provided to digitize the input signals. Each converter runs with 20.25 MHz and has 8-bit resolution. An integrated bandgap circuit generates the required reference voltages for the converters. The two ADCs are of a 2-stage subranging type.

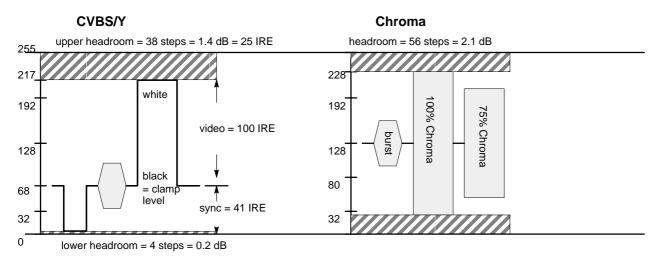

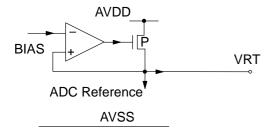

# 2.1.5. ADC Range

The ADC input range for the various input signals and the digital representation is given in Table 2–1 and Fig. 2–2. The corresponding output signal levels of the VPX 32xx are also shown.

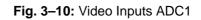

## 2.1.6. Digitally Controlled Clock Oscillator

The clock generation is also a part of the analog front end. The crystal oscillator is controlled digitally by the FP; the clock frequency can be adjusted within  $\pm 150$  ppm.

Fig. 2-1: Analog front-end

| Signal |              | Input Level [mV <sub>pp</sub> ] |      |         | ADC<br>Range | YC <sub>r</sub> C <sub>b</sub><br>Output<br>Range |

|--------|--------------|---------------------------------|------|---------|--------------|---------------------------------------------------|

|        |              | –6 dB                           | 0 dB | +4.5 dB | [steps]      | [steps]                                           |

| CVBS   | 100% CVBS    | 667                             | 1333 | 2238    | 252          | -                                                 |

|        | 75% CVBS     | 500                             | 1000 | 1679    | 213          | -                                                 |

|        | video (luma) | 350                             | 700  | 1175    | 149          | 224                                               |

|        | sync height  | 150                             | 300  | 504     | 64           | -                                                 |

|        | clamp level  |                                 |      |         | 68           | 16                                                |

| Chroma | burst        |                                 | 300  |         | 64           | -                                                 |

|        | 100% Chroma  |                                 | 890  |         | 190          | $128\pm112$                                       |

|        | 75% Chroma   |                                 | 670  |         | 143          | 128±84                                            |

|        | bias level   |                                 |      |         | 128          | 128                                               |

# Table 2–1: ADC input range for PAL input signal and corresponding output signal ranges

Fig. 2-2: ADC ranges for CVBS/Luma and Chroma, PAL input signal

#### 2.2. Color Decoder

In this block, the standard luma/chroma separation and multi-standard color demodulation is carried out. The color demodulation uses an asynchronous clock, thus allowing a unified architecture for all color standards.

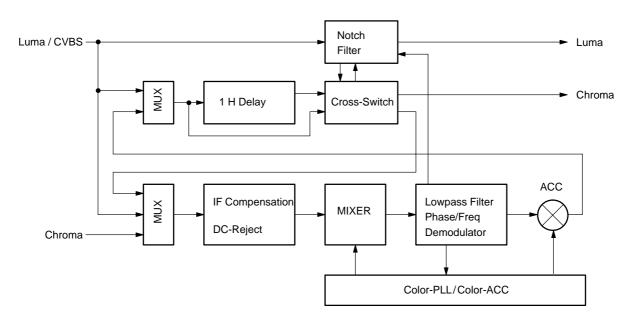

A block diagram of the color decoder is shown in Fig. 2–4. The luma, as well as the chroma processing, is shown here. The color decoder also provides several special modes; for example, wide band chroma format which is intended for S-VHS wide bandwidth chroma. Also, filter settings are available for processing a PAL+ helper signal.

If the adaptive comb filter is used for luma chroma separation, the color decoder uses the S-VHS mode processing. The output of the color decoder is  $YC_rC_b$  in a 4:2:2 format.

## 2.2.1. Demodulator

The entire signal (which might still contain luma) is now quadrature-mixed to the baseband. The mixing frequency is equal to the subcarrier for PAL and NTSC, thus achieving the chroma demodulation. For SECAM, the mixing frequency is 4.286 MHz giving the quadrature baseband components of the FM modulated chroma. After the mixer, a lowpass filter selects the chroma components; a downsampling stage converts the color difference signals to a multiplexed half rate data stream.

The subcarrier frequency in the demodulator is generated by direct digital synthesis; therefore, substandards such as PAL 3.58 or NTSC 4.43 can also be demodulated.

#### 2.2.2. IF-Compensation

With off-air or mistuned reception, any attenuation at higher frequencies or asymmetry around the color subcarrier is compensated. Four different settings of the IFcompensation are possible:

- flat (no compensation)

- 6 dB/octave

- 12 dB/octave

- 10 dB/MHz

The last setting gives a very large boost to high frequencies. It is provided for SECAM signals that are decoded using a SAW filter specified originally for the PAL standard.

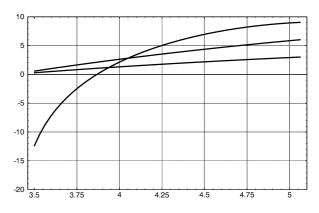

Fig. 2–3: Frequency response of chroma IF-compensation

#### Fig. 2–4: Color decoder

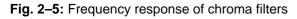

## 2.2.3. Chrominance Filter

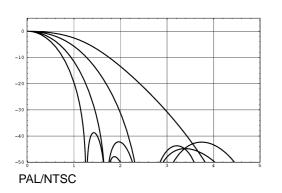

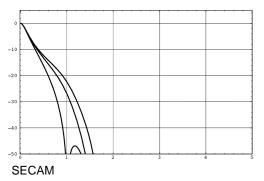

The demodulation is followed by a lowpass filter for the color difference signals for PAL/NTSC. SECAM requires a modified lowpass function with bell-filter characteristic. At the output of the lowpass filter, all luma information is eliminated.

The lowpass filters are calculated in time multiplex for the two color signals. Four bandwidth settings (narrow, normal, broad, wide) are available for each standard. The filter passband can be shaped with an extra peaking term at 1.25 MHz. For PAL/NTSC, a wide band chroma filter can be selected. This filter is intended for high bandwidth chroma signals; for example, a nonstandard wide bandwidth S-VHS signal.

#### 2.2.4. Frequency Demodulator

The frequency demodulator for demodulating the SE-CAM signal is implemented as a CORDIC-structure. It calculates the phase and magnitude of the quadrature components by coordinate rotation.

The phase output of the CORDIC processor is differentiated to obtain the demodulated frequency. After a programmable deemphasis filter, the Dr and Db signals are scaled to standard  $C_rC_b$  amplitudes and fed to the crossover-switch.

**Fig. 2–6:** Frequency response of SECAM-deemphasis

## 2.2.5. Burst Detection

In the PAL/NTSC-system, the burst is the reference for the color signal. The phase and magnitude outputs of the CORDIC are gated with the color key and used for controlling the phase-lock-loop (APC) of the demodulator and the automatic color control (ACC) in PAL/NTSC.

The ACC has a control range of +30...-6 dB.

For SECAM decoding, the frequency of the burst is measured. Thus, the current chroma carrier frequency can be identified and is used to control the SECAM processing. The burst measurements also control the color killer operation; they can be used for automatic standard detection as well.

## 2.2.6. Color Killer Operation

The color killer uses the burst-phase/burst-frequency measurement to identify a PAL/NTSC or SECAM color signal. For PAL/NTSC, the color is switched off (killed) as long as the color subcarrier PLL is not locked. For SE-CAM, the killer is controlled by the toggle of the burst frequency. The burst amplitude measurement is used to switch off the color if the burst amplitude is below a programmable threshold. Thus, color will be killed for very noisy signals. The color amplitude killer has a programmable hysteresis.

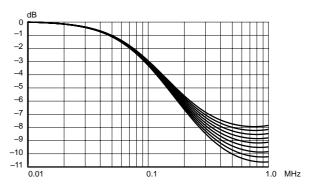

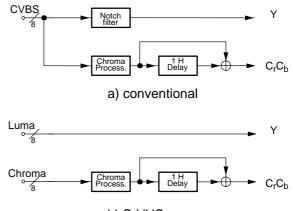

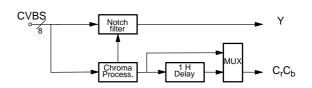

## 2.2.7. PAL Compensation/1-H Comb Filter

The color decoder uses one fully integrated delay line. Only active video is stored.

The delay line application depends on the color standard:

- NTSC: 1-H comb filter **or** color compensation

- PAL: color compensation

- SECAM: crossover-switch

In the NTSC compensated mode, Fig. 2–7 c), the color signal is averaged for two adjacent lines. Thus, cross-color distortion and chroma noise is reduced. In the NTSC combfilter mode, Fig. 2–7 d), the delay line is in the composite signal path, thus allowing reduction of cross-color components, as well as cross-luminance. The loss of vertical resolution in the luminance channel is compensated by adding the vertical detail signal with removed color information.

Fig. 2–9: SECAM color decoding

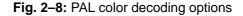

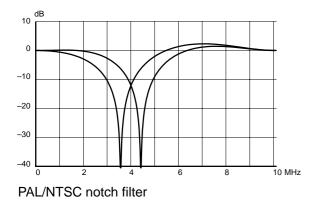

## 2.2.8. Luminance Notch Filter

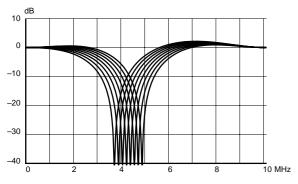

If a composite video signal is applied, the color information is suppressed by a programmable notch filter. The position of the filter center frequency depends on the subcarrier frequency for PAL/NTSC. For SECAM, the notch is directly controlled by the chroma carrier frequency. This considerably reduces the cross-luminance. The frequency responses for all three systems are shown in Fig. 2–10. In S-VHS mode, this filter is bypassed.

SECAM notch filter

Fig. 2–10: Frequency responses of the luma notch filter for PAL, NTSC, SECAM

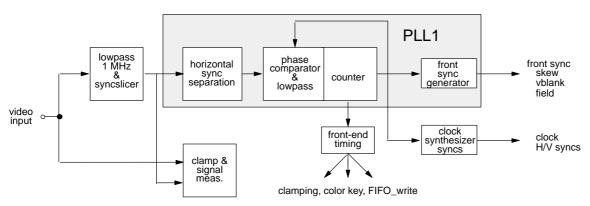

#### 2.3. Video Sync Processing

Fig. 2–11 shows a block diagram of the front-end sync processing. To extract the sync information from the video signal, a linear phase lowpass filter eliminates all noise and video contents above 1 MHz. The sync is separated by a slicer; the sync phase is measured. The internal controller can select variable windows to improve the noise immunity of the slicer. The phase comparator measures the falling edge of sync, as well as the integrated sync pulse.

The sync phase error is filtered by a phase-locked loop that is computed by the FP. All timing in the front-end is derived from a counter that is part of this PLL, and it thus counts synchronously to the video signal.

A separate hardware block measures the signal back porch and also allows gathering the maximum/minimum of the video signal. This information is processed by the FP and used for gain control and clamping.

For vertical sync separation, the sliced video signal is integrated. The FP uses the integrator value to derive vertical sync and field information.

Frequency and phase characteristics of the analog video signal are derived from PLL1. The results are fed to the rest of the video processing system in the backend. The resizer unit uses them for data interpolation and orthogonalization. A separate timing block derives the timing reference signals HREF and VREF from the horizontal sync.

Fig. 2–11: Sync separation block diagram

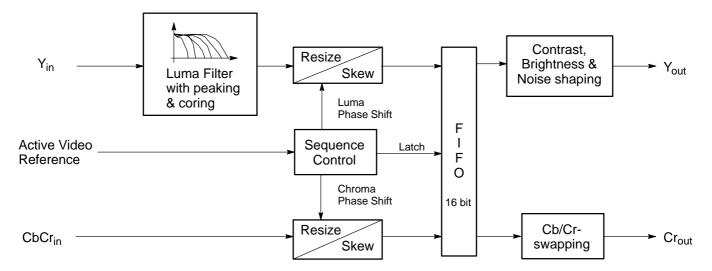

## 2.4. Component Processing

Recovery of the YCbCr components by the decoder is followed by horizontal resizing and skew compensation. Contrast enhancement with noise shaping can also be applied to the luminance signal.

Fig. 2–12 illustrates the signal flow through the component processing stage. The YCbCr 4:2:2 samples are separated into a luminance path and a chrominance path. The Luma Filtering block applies anti-aliasing lowpass filters with cutoff frequencies adapted to the number of samples after scaling, as well as peaking and coring. The Resize and Skew blocks alter the effective sampling rate and compensate for horizontal line skew. The YCbCr samples are buffered in a FIFO for continuous burst at a fixed clock rate. For luminance samples, the contrast and brightness can be adjusted and noise shaping applied. In the chrominance path, Cb and Cr samples can be swapped. Without swapping, the first valid video sample is a Cb sample. Chrominance gain can be adjusted in the color decoder.

Fig. 2–12: Component processing stage

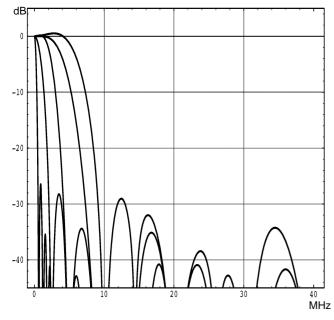

#### 2.4.1. Horizontal Resizer

The horizontal resizer alters the sampling raster of the video signal, thereby varying the number of pixels (NPix) in the active portion of the video line. The number of pixels per line is selectable within a range from 32 to 864 in increments of 2 pixels (see section 2.8.: Windowing the video field). Table 2–2 gives an overview of several supported video rasters. The visual quality of a sampling rate conversion operation depends on two factors:

- the frequency response of the individual filters, and

- the number of available filters from which to choose.

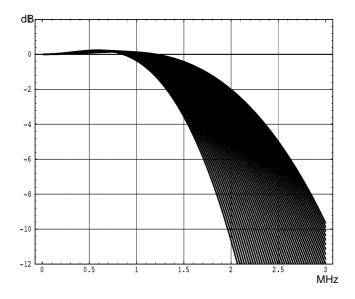

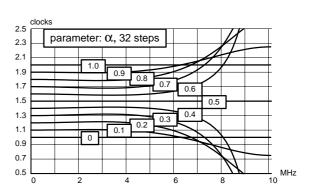

The VPX is equipped with a battery of FIR filters to cover the five octave operating range of the resizer. Fig. 2–13 shows the magnitude response of five example filters corresponding to 1054, 526, 262, 130, and 32 pixels.

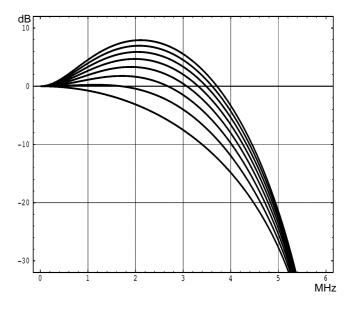

The density of the filter array can be seen in Fig. 2–14. The magnitude response of 50 filters lying next to each other are shown. Nevertheless, these are only 10% of all filters shown. As a whole, the VPX comes with a battery of 512 FIR filters. Showing these 512 Filters in Fig. 2–13 would result in a large black area. This dense array of filters is necessary in order to maintain constant visual quality over the range of allowable picture sizes. The alternative would be to use a small number of filters whose cutoff frequencies are regularly spaced over the spectrum. However, it has been found that using few filters leads to visually annoying threshold behavior. These effects occur when the filters are changed in response to variations in the picture size.

Filter selection is performed automatically by the internal processor based on the selected resizing factor (NPix). This automated selection is optimized for best visual performance.

Fig. 2–13: Magnitude response of five widely spaced filters

Fig. 2–14: Magnitude response of 50 neighbored filters

Fig. 2–15: Magnitude response of one peaking filter

#### 2.4.2. Skew Correction

The VPX delivers orthogonal pixels with a fixed clock even in the case of non-broadcast signals with substantial horizontal jitter (VCRs, laser disks, certain portions of the 6 o'clock news...).

This is achieved by highly accurate sync slicing combined with post correction. Immediately after the analog input is sampled, a horizontal sync slicer tracks the position of sync. This slicer evaluates, to within 1.6 ns, the skew between the sync edge and the edge of the pixelclock. This value is passed as a skew on to the phase shift filter in the resizer. The skew is then treated as a fixed initial offset during the resizing operation.

The **Skew** block in the resizer performs programmable phase shifting with subpixel accuracy. In the luminance path, a linear interpolation filter provides a phase shift between 0 and 31/32 in steps of 1/32. This corresponds to an accuracy of 1.6 ns. The chrominance signal can be shifted between 0 and 7/8 in steps of 1/8. Figs. 2–16 through 2–19 show the transfer function of the two skew filters.

**Fig. 2–16:** Luminance skew filter magnitude frequency response

**Fig. 2–18:** Chrominance skew filter magnitude frequency response

**Fig. 2–17:** Luminance skew filter group delay characteristics

Fig. 2–19: Chrominance skew filter group delay characteristics

| NTSC      | PAL/SECAM | Format Name                                         |  |  |

|-----------|-----------|-----------------------------------------------------|--|--|

| 640 x 480 | 768 x 576 | Square pixels for broadcast TV (4:3)                |  |  |

| 704 x 480 | 704 x 576 | Input Raster for MPEG-2                             |  |  |

| 320 x 240 | 384 x 288 | Square pixels for TV (quarter resolution)           |  |  |

| 352 x 240 | 352 x 288 | CIF – Input raster for MPEG-1, H.261                |  |  |

| 160 x 120 | 192 x 144 | Square pixels for TV (1/16 resolution), H.324,H.323 |  |  |

| 176 x 120 | 176 x 144 | QCIF – Input raster for H.261                       |  |  |

| 32 x 24   | 32 x 24   | Video icons for graphical interfaces (square)       |  |  |

Table 2-2: Several rasters supported by the resizer

# 2.4.3. Peaking and Coring

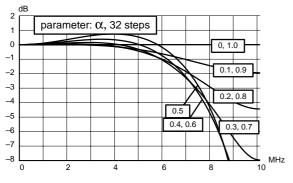

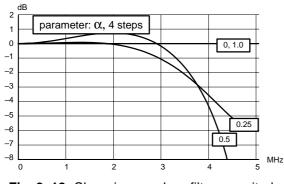

The horizontal resizer comes with an extra peaking filter for sharpness control. The center frequency of the peaking filter is automatically adjusted to the image size in 512 steps. The peaking value to each center frequency can be controlled by the user with up to eight steps via FP-RAM 0x126/130. Fig. 2–15 shows the magnitude response of the eight steps of the peaking filter corresponding to an image size of 320 pixels.

After the peaking filter, an additional coring filter is implemented to the horizontal resizer. The coring filter subtracts 0, 1/2, 1, or 2 LSBs of the higher frequency part of the signal. Note, that coring can be performed independently of the peaking value adjustment.

The operating range of the horizontal resizer was chosen to serve the widest possible range of applications and source formats (number of lines, aspect ratio, etc...). Table 2–2 lists several examples for video sourced from 525/625 line TV systems. Vertical resizing is supported via line dropping.

# 2.4.4. YCbCr Color Space

The color decoder outputs luminance and one multiplexed chrominance signal at a sample clock of 20.25 MHz. Active video samples are flagged by a separate reference signal. Internally, the number of active samples is 1080 for all standards (525 lines and 625 lines). The representation of the chroma signals is the ITU-R 601 digital studio standard.

In the color decoder, the weighting for both color difference signals is adjusted individually. The default format has the following specification:

-Y = 224\*Y + 16 (pure binary),

- $-C_r = 224^*(0.713^*(R-Y)) + 128$  (offset binary),

- $C_b = 224^*(0.564^*(B-Y)) + 128$  (offset binary).

# 2.4.5. Video Adjustments

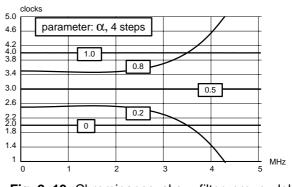

The VPX provides a selectable gain (contrast) and offset (brightness) for the luminance samples, as well as additional noise shaping. Both the contrast and brightness factors can be set externally via I<sup>2</sup>C serial control of FP-RAM 0x127,128,131, and 132. Fig. 2–20 gives a functional description of this circuit. First, a gain is applied, yielding a 10-bit luminance value. The conversion back to 8-bit is done using one of four selectable techniques: simple rounding, truncation,1-bit error diffusion, or 2-bit error diffusion. Bit[8] in the 'contrast'-register selects between the clamping levels 16 and 32.

$$I_{out} = c * I_{in} + b$$

$c = 0...63/32$  in 64 steps

b = -127...128 in 256 steps

In the chrominance path, Cb and Cr samples can be swapped with bit[8] in FP-RAM 0x126 or 130. Adjustment of color saturation and gain is provided via FP-RAM 0x30–33 (see section 2.2.5.).

Fig. 2-20: Contrast and brightness adjustment

# 2.5. Video Output Interface

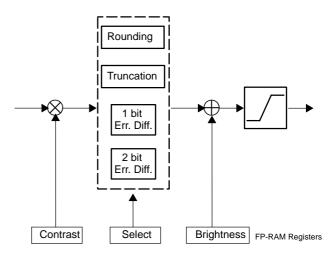

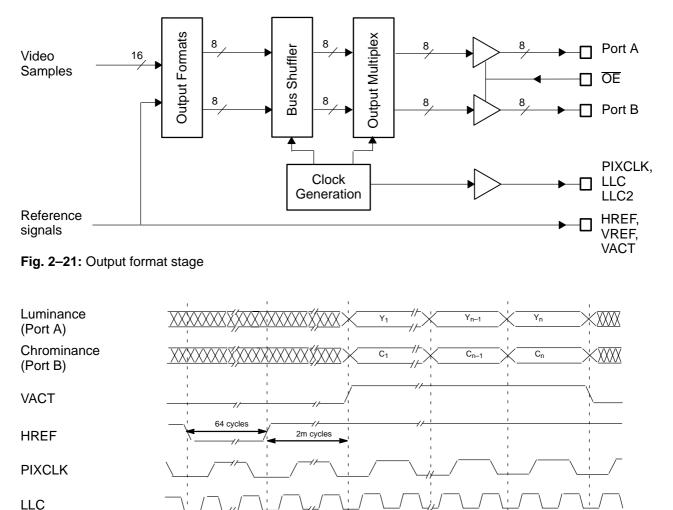

Contrary to the component processing stage running at a clock rate of 20.25 MHz, the output formatting stage (Fig. 2–21) receives the video samples at a pixel transport rate of 13.5 MHz. It supports 8 or 16-bit video formats with separate or embedded reference signals, provides bus shuffling, and channels the output via one or both 8-bit ports. Data transfer is synchronous to the internally generated 13.5 MHz pixel clock.

The format of the output data depends on three parameters:

- the selected output format

- YUV 4:2:2, separate syncs

- YUV 4:2:2, ITU-R656

- YUV 4:2:2, embedded reference codes (BStream)

- the number of active ports (A only, or both A and B)

- clock speed (single or double).

In 8-bit modes using only Port A for video data, Port B can be used as programmable output.

# 2.5.1. Output Formats

The VPX supports the YUV 4:2:2 video format only. During normal operation, all reference signals are output separately. To provide a reduced video interface, the VPX offers two possibilities for encoding timing references into the video data stream: an ITU-R656 compliant output format with embedded timing reference headers and a second format with single timing control codes in the video stream. The active output format can be selected via FP-RAM 0x150 [format].

# 2.5.1.1. YUV 4:2:2 with Separate Syncs/ITU-R601

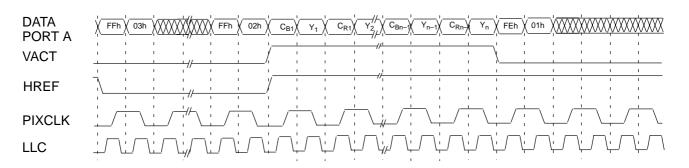

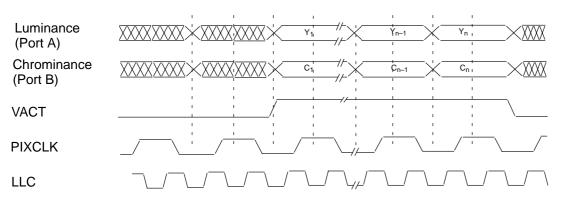

The default output format of the VPX is a synchronous 16-bit YUV 4:2:2 data stream with separate reference signals. Port A is used for luminance and Port B for chrominance-information. Video data is compliant to ITU-R601. Bit[1:0] of FP-RAM 0x150 has to be set to 00. Figure 2–22 shows the timing of the data ports and the reference signals in this mode.

Fig. 2-22: Detailed video output; single clock mode

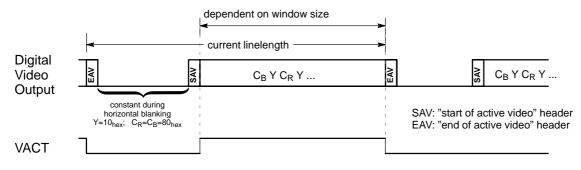

#### 2.5.1.2. Embedded Reference Headers/ITU-R656

The VPX supports an output format which is designed to be compliant with the ITU-R656 recommendation. It is activated by setting Bit[1:0] of FP-RAM 0x150 to 01. The 16-bit video data must be multiplexed to 8 bit at the double clock frequency (27 MHz) via FP-RAM 0x154, bit 9 set to 1 (see also section 2.5.3.: Output Multiplexer).

In this mode, video samples are in the following order: **Cb**, **Y**, **Cr**, **Y**, ... The data words 0 and 255 are protected since they are used for identification of reference headers. This is assured by limitation of the video data. Timing reference codes are inserted into the data stream at the beginning and the end of each video line in the following way: A 'Start of active video'-Header (SAV) is inserted before the first active video sample. The 'end of active video'-code (EAV) is inserted after the last active video sample. They both contain information about the field type and field blanking. The data words occuring during the horizontal blanking interval between EAV and SAV are filled with 0x10 for luminance and 0x80 for chrominance information. Table 2–3 shows the format of the SAV and EAV header.

Note that the following changes and extensions to the ITU-R656 standard have been included to support horizontal and vertical scaling, transmission of VBI-data, etc.:

- Both the length and the number of active video lines varies with the selected window parameters. For compliance with the ITU-R656 recommendation, a size of 720 samples per line must be selected for each window. To enable a constant line length even in the case of different scaling values for the video windows, the VPX provides a programmable 'active video' signal (see section 2.7.4.).

- During blanked lines, the VACT signal will be suppressed. VBI-lines can be marked as blanked or active lines, thus allowing the choice of enabled or suppressed VACT during the VBI-window. Note that the vertical field blanking flag (V) in the SAV/EAV header is set to zero in any line with enabled VACT signal (valid VBI or video lines).

- For data within the VBI-window (e.g. sliced or raw teletext data), the user can select between limitation or reduction to 7-bit resolution with an additional least significant bit assuring odd parity (0 and 255 never occur). This option can be selected via FP-RAM 0x150 [range].

| Word                                   | MSE                                                                              | Bit No.<br>MSB LSB |   |   |       |    |    |    |

|----------------------------------------|----------------------------------------------------------------------------------|--------------------|---|---|-------|----|----|----|

|                                        | 7                                                                                | 6                  | 5 | 4 | 3     | 2  | 1  | 0  |

| First                                  | 1                                                                                | 1                  | 1 | 1 | 1     | 1  | 1  | 1  |

| Second                                 | 0                                                                                | 0                  | 0 | 0 | 0     | 0  | 0  | 0  |

| Third                                  | 0                                                                                | 0                  | 0 | 0 | 0     | 0  | 0  | 0  |

| Fourth                                 | 1                                                                                | F                  | V | н | P3    | P2 | P1 | P0 |

| F = 0 duri<br>V = 0 else<br>H = 0 in S | ng field 1, F = 1 during field 2<br>ewhere, V = 1 during vertical field blanking |                    |   |   | nking |    |    |    |

Table 2-3: Coding of the SAV/EAV-header

The bits P0, P1, P2, and P3 are protection bits. Their states are dependent on the states of F, V, and H as shown in table 2–4.

| Table 2–4: Coding of the protection bi |

|----------------------------------------|

|----------------------------------------|

| F | v | н | P3 | P2 | P1 | P0 |

|---|---|---|----|----|----|----|

| 0 | 0 | 0 | 0  | 0  | 0  | 0  |

| 0 | 0 | 1 | 1  | 1  | 0  | 1  |

| 0 | 1 | 0 | 1  | 0  | 1  | 1  |

| 0 | 1 | 1 | 0  | 1  | 1  | 0  |

| 1 | 0 | 0 | 0  | 1  | 1  | 1  |

| 1 | 0 | 1 | 1  | 0  | 1  | 0  |

| 1 | 1 | 0 | 1  | 1  | 0  | 0  |

| 1 | 1 | 1 | 0  | 0  | 0  | 1  |

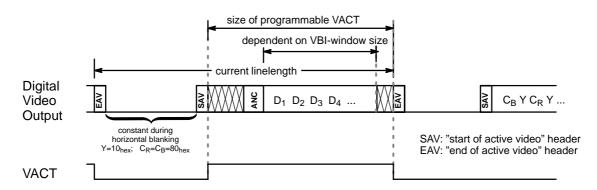

The VPX also supports the transmission of VBI-data as vertical ancillary data during blanked lines in the interval starting with the end of the SAV and terminating with the beginning of EAV. In this case, an additional header is inserted directly before the valid active data. In this mode, the position of SAV and EAV depends on the settings for the programmable VACT signal. These parameters will be checked and corrected if necessary to assure an appropriate size of VACT for both data and ancillary header.

|        |     | Bit No. |    |    |    |    |    |             |

|--------|-----|---------|----|----|----|----|----|-------------|

| Word   | MSE | 3       |    |    |    |    |    | LSB         |

|        | 7   | 6       | 5  | 4  | 3  | 2  | 1  | 0           |

| First  | 0   | 0       | 0  | 0  | 0  | 0  | 0  | 0           |

| Second | 1   | 1       | 1  | 1  | 1  | 1  | 1  | 1           |

| Third  | 1   | 1       | 1  | 1  | 1  | 1  | 1  | 1           |

| Fourth | 0   | T6      | T5 | T4 | Т3 | T2 | T1 | odd         |

| Fifth  | 0   | M6      | M5 | M4 | М3 | M2 | M1 | par-<br>ity |

| Sixth  | 0   | L6      | L5 | L4 | L3 | L2 | L1 | ity         |

Table 2–5: Coding of the ancillary header information

Table 2–5 shows the coding of the ancillary header information. The word T[6:1] contains a value for data type identification (1 for sliced data, 2 for raw data). M[6:1] contains the MSBs and L[6:1] the LSBs of the number of following words (128 for sliced data, 1140 for raw data). Note that the following video data is either limited or has odd parity to assure that 0 and 255 will not occur. Bit 3 in RAM 0x150 selects between these two options.

Fig. 2-23: Output of video or VBI data with embedded reference headers (according to ITU-R656)

Fig. 2-24: Detailed video output; double clock on

Fig. 2-25: Output of VBI-data as ancillary data

# 2.5.1.3. Embedded Timing Codes (BStream)

In this mode, several event words are inserted into the pixel stream for timing information. It is activated by setting Bit[1:0] of FP-RAM 0x150 to 10. Each event word consists of a chrominance code value containing the phase of the color-multiplex followed by a luminance code value signalling a specific event. The allowed control codes are listed in table 2–6 and 2–7.

At the beginning and the end of each active video line, timing reference codes (start of active video: SAV; end of active video: EAV) are inserted with the beginning and the end of VACT. Since VACT is suppressed during blanked lines, video data and SAV/EAV codes are present during active lines only. If raw/sliced data should be output, VACT has to be enabled during the VBI window with bit 2 of FP-RAM 0x138! In the case of several windows per field, the length of the active data stream per line can vary. Since the qualifiers for active video (SAV/ EAV) are independent of the other reference codes, there is no influence on horizontal or vertical syncs, and sync generation can be performed even with several different windows. For full compliance with applications requiring data streams of a constant size, the VPX provides a mode with programmable 'video active' signal VACT which can be selected via bit 2 of FP-RAM 0x140. The start and end positions of VACT relative to HREF is determined by FP-RAM 0x151 and 0x152. The delay of valid data relative to the leading edge of HREF is calculated with the formulas given in table 2-8 and 2-9. The result can be read in FP-RAM 0x10f (for window 1) and 0x11f (for window 2). Be aware that the largest window defines the size of the needed memory. In the case of 1140 raw VBI-samples and only 32 scaled video samples, the graphics controller needs 570 words for each line (the VBI-samples are multiplexed to luminance and chrominance paths).

The leading edge of HREF indicates the beginning of a new video line. Depending on the type of the current line

(active or blanked), the corresponding horizontal reference code is inserted. For big window sizes, the leading edge of HREF can arrive before the end of the active data. In this case, hardware assures that the control code for HREF is delayed and inserted after EAV only. The VREF control code is inserted at the falling edge of VREF. The state of HREF at this moment indicates the current field type (HREF = 0: odd field; HREF = 1: even field).

In this mode, the words 0,1,254, and 255 are reserved for data identifications. This is assured by limitation of the video data.

Table 2-6: Chrominance control codes

| Chroma Value | Phase Information |

|--------------|-------------------|

| FE           | Cr pixel          |

| FF           | Cb pixel          |

#### 2.5.2. Bus Shuffler

In the YUV 4:2:2 mode, the output of luminance data is on port A and chrominance data on Port B. With the bus shuffler, luminance can be switched to Port B and chrominance to port A. In 8-bit double clock mode, shuffling can be used to swap the Y and C components. It is selected with FP-RAM 0x150.

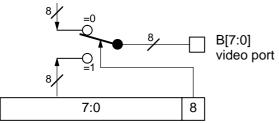

## 2.5.3. Output Multiplexer

During normal operation, a 16-bit YUV 4:2:2 data stream is transferred synchronous to an internally generated PIXCLK at a rate of 13.5 MHz. Data can be latched onto the falling edge of PIXCLK or onto the rising edge of LLC

| Luma<br>Value | Video Event      | Video Event                          | Phase Information           |

|---------------|------------------|--------------------------------------|-----------------------------|

| 01            | VACT end         | last pixel was the last active pixel | refers to the last pixel    |

| 02            | VACT begin       | next pixel is the first active pixel | refers to the next pixel    |

| 03            | HREF active line | begin of an active video line        | refers to the current pixel |

| 04            | HREF blank line  | begin of a blank line                | refers to the current pixel |

| 05            | VREF even        | begin of an even field               | refers to the current pixel |

| 06            | VREF odd         | begin of an odd field                | refers to the current pixel |

Table 2–7:

Luminance control codes

during high PIXCLK. In the double clock mode, luminance and chrominance data are multiplexed to 8 bit and transferred at the double clock frequency of 27 MHz in the order Cb, Y, Cr, Y...; the first valid chrominance value being a Cb sample. With shuffling switched on, Y and C components are swapped. Data can be latched with the rising edge of LLC or alternating edges of PIXCLK. This mode is selected with bit 9 of FP-RAM 0x154. All 8-bit modes use Port A only. In this case, Port B can be activated as programmable output with bit 8 of FP-RAM 0x154. Bit 0–7 determine the state of Port B.

video data

FP-RAM 0x154 [outmux]

#### Fig. 2-26: Programmable output port

#### 2.5.4. Output Ports

The two 8-bit ports produce TTL level signals coded in binary offset. The Ports can be tristated either via the output enable pin ( $\overline{OE}$ ) or via I<sup>2</sup>C register 0xF2. For more information, see section 2.16. "Enable/Disable of Output Signals".

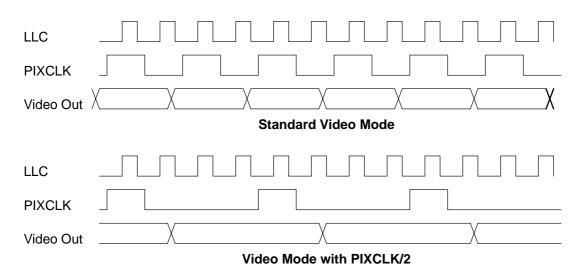

#### 2.5.5. Half-Clock Mode

For applications demanding a low bandwidth for the transmission between video decoder and graphics controller, the clock signal qualifying the output pixels (PIXCLK) can be divided by 2. This mode is enabled by setting Bit 5 of the FP-RAM 0x150 [halfclk]. Note that the output format ITU-R601 must be selected. The timing of the data and clock signals in this case is described in Figure 2–28.

If the PIXCLK/2 mode is enabled, each second pulse of PIXCLK is gated. PIXCLK can be used as a qualifier for valid data. To ensure that the video data stream can be spread, the selected number of valid output samples should not exceed 400.

#### Fig. 2–28: Timing in the half-clock mode

#### 2.6. Video Data Transfer

The VPX supports a synchronous video interface. Video data arrives to each line at the output in an uninterrupted burst with a fixed transport rate of 13.5 MHz. The duration of the burst is measured in clock periods of the transport clock and is equal to the number of pixels per output line.

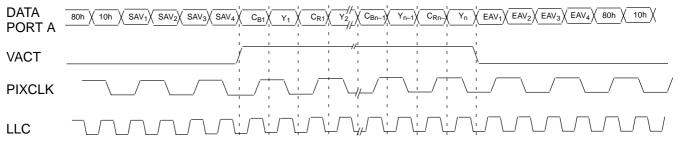

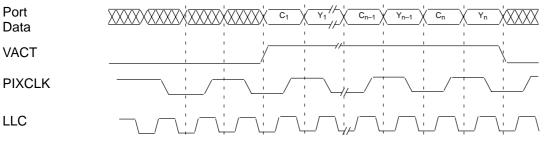

The data transfer is controlled via three signals: PIXCLK, VACT, and LLC.

Data is transferred synchronous to the internally generated PIXCLK. The frequency of PIXCLK is 13.5 MHz. The LLC signal is provided as an additional support for both the 13.5 MHz and the 27 MHz double clock mode. The LLC consists of a doubled PIXCLK signal (27 MHz) for interface to external components which rely on the Philips transfer protocols. In the single clock mode, data can be latched onto the falling edge of PIXCLK or at the rising edge of LLC during high PIXCLK. In double clock mode, output data can be latched onto both clock edges of PIXCLK or onto every rising edge of LLC. Combined with the half-clock mode, the available transfer bandwidths at the ports are therefore 6.75 MHz, 13.5 MHz, and 27.0 MHz.

The VACT signal flags the presence of valid output data. Fig. 2–29 and 2–30 illustrate the relationship between the video port data, VACT, PIXCLK, and LLC. Whenever a line of video data should be suppressed (line dropping, switching between analog inputs), it is done by suppression of VACT.

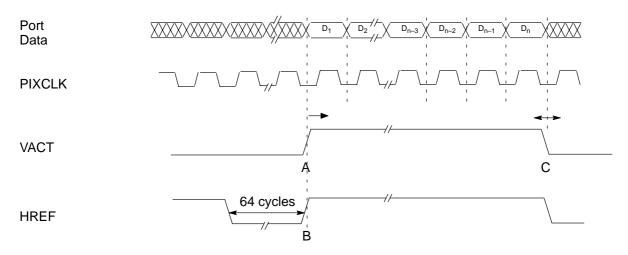

Fig. 2–31 illustrates the temporal relationship between the VACT and the HREF signals as a function of the number of pixels per output line and the horizontal dimensions of the window. The duration of the inactive period of the HREF (Fig. 2–31) is fixed. Tables 2–8 and 2–9 show the formulas for the position of valid data samples relative to the trailing edge of HREF, while table 2–10 gives an overview of the relation for different cases. The calculated delay can be read via FP-RAM 0x10f (window 1) or 0x11f (window2).

Fig. 2–30: Timing in double clock mode (bus shuffler off)

| Mode            | Data Delay                                                                  | Data End         |

|-----------------|-----------------------------------------------------------------------------|------------------|

| Video data      | (HBeg+HLen)*(720/NPix)–Hlen for NPix<720<br>HBeg*(720/NPix) for NPix >= 720 | DataDelay + HLen |

| Raw VBI data    | 150                                                                         | 720              |

| Sliced VBI data | 726                                                                         | 790              |

Table 2-8: Delay of video data relative to the trailing edge of HREF (mode with full PIXCLK)

# Table 2–9: Delay of video data relative to the trailing edge of HREF in PIXCLK/2 mode

| Mode            | Data Delay                                                                    | Data End           |

|-----------------|-------------------------------------------------------------------------------|--------------------|

| Video data      | (HBeg+HLen)*(720/NPix)–2*Hlen for NPix<360<br>HBeg*(720/NPix) for NPix >= 360 | DataDelay + 2*HLen |

| Raw VBI data    | not possible!                                                                 | not possible!      |

| Sliced VBI data | 662                                                                           | 790                |

## Table 2–10: Relationship between HREF and VACT

| Resizing   | Windowing        | Timing of rising edges | Timing of falling edges |

|------------|------------------|------------------------|-------------------------|

| NPix = 720 |                  | A = 0                  | C = 720                 |

| 720 < NPix | none             | A = 0                  | C > 720                 |

| NPix < 720 |                  | A > 0                  | C = 720                 |

| NPix ≤ 720 | windowbegin/-end | A = windowbegin > 0    | C = 720                 |

| NPix ≥ 720 | windowbegin/-end | A= windowbegin > 0     | C = windowend           |

Fig. 2–31: Relation between HREF and VACT signals

## 2.7. Video Reference Signals

The complete video interface of the VPX runs at a clock rate of 13.5 MHz. It mainly generates two reference signals for the video timing: a horizontal reference (HREF) and a vertical reference (VREF). These two signals are generated by programmable hardware and can be either free running or synchronous to the analog input video. The video line standard (625/50 or 525/60) depends on the TV-standard selected with FP-RAM 0x20 [sdt]. The polarity of both signals is individually selectable via FP-RAM 0x153.

The circuitry which produces the VREF and HREF signals has been designed to provide a stable, robust set of timing signals, even in the case of erratic behavior at the analog video input. Depending on the selected operating mode given in FP-RAM 0x140 [settm], the period of the HREF and VREF signals are guaranteed to remain within a fixed range. These video reference signals can therefore be used to synchronize the external components of a video subsystem (for example the ICs of a PC add-in card).

In addition to the timing references, valid video samples are marked with the 'video active' qualifier (VACT). In order to reduce the signal number of the video interface, several 8-bit modes have been implemented, where the reference signals are multiplexed into the data stream (see section 2.5.1.).

## 2.7.1. HREF

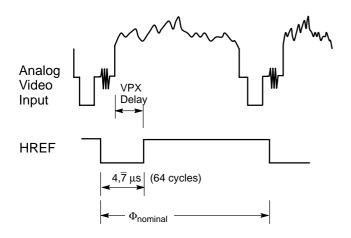

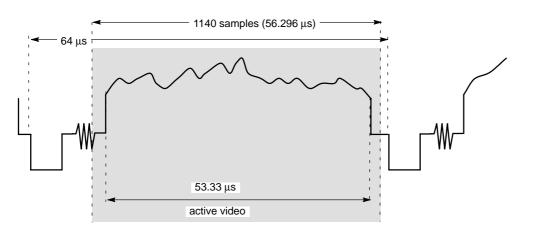

Fig. 2–32 illustrates the timing of the HREF signal relative to the analog input. The inactive period of HREF has a fixed length of 64 periods of the 13.5 MHz output clock rate. The total period of the HREF signal is expressed as  $\Phi_{\rm nominal}$  and depends on the video line standard.

Fig. 2-32: HREF relative to Input Video

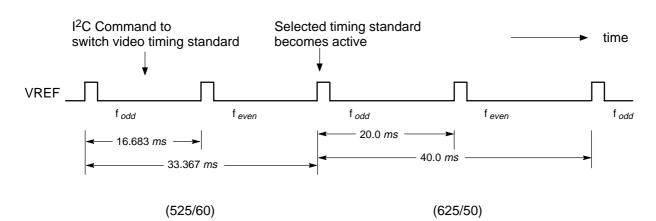

## 2.7.2. VREF

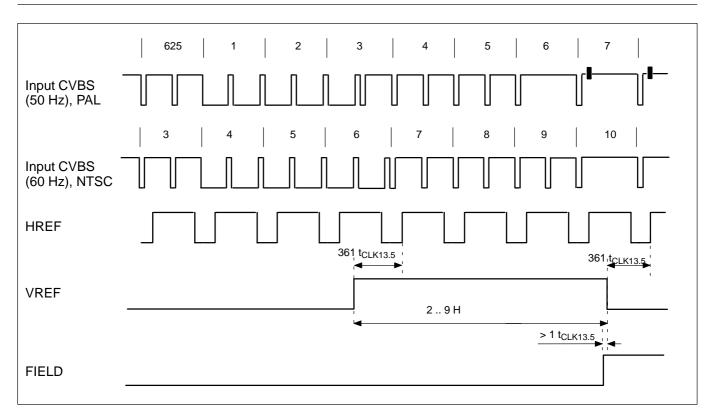

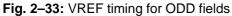

Figs. 2–33 and 2–34 illustrate the timing of the VREF signal relative to field boundaries of the two TV standards. The start of the VREF pulse is fixed, while the length is programmable in the range between 2 and 9 video lines via FP-RAM 0x153 [vlen].

# 2.7.3. Odd/Even Information (FIELD)

Information on whether the current field is odd or even is supplied through the relationship between the edge (either leading or trailing) of VREF and level of HREF. This relationship is fixed and shown in Figs. 2–33 and 2–34. The same information can be supplied to the FIELD pin, which can be enabled/disabled as output in FP-RAM 0x153 [enfieldq]. FP-RAM 0x153 [oepol] programs the polarity of this signal.

During normal operation the FIELD flag is filtered since most applications need interlaced signals. After filtering, the field type is synchronized to the input signal only if the last 8 fields have been alternating; otherwise, it always toggles. This filtering can be disabled with FP-RAM 0x140 [disoef]. In this case, the field information follows the odd/even property of the input video signal.

## 2.7.4. VACT

The 'video active' signal is a qualifier for valid video samples. Since scaled video data is stored internally, there are no invalid pixel within the VACT interval. VACT has a defined position relative to HREF depending on the window settings (see section 2.8.). The maximal window length depends on the minimal line length of the input signal. It is recommended to choose window sizes of less than 800 pixels. Sizes up to 864 are possible, but for non-standard input lines, VACT is forced inactive 4 PIXCLK cycles before the next trailing edge of HREF.

During the VBI-window, VACT can be enabled or suppressed with FP-RAM 0x138. Within this window, the VPX can deliver either sliced text data with a constant length of 64 samples or 1140 raw input samples. For applications that request a uniform window size over the whole field, a mode with a free programmable VACT is supported [FP-RAM 0x140, vactmode]. The start and end position for the VACT signal relative to the trailing edge of HREF can be programmed within a range of 0 to 864 [FP-RAM 0x151, 0x152]. In this case, VACT no longer marks valid samples only. The position of the valid data depends on the window definitions. It is calculated from the internal processor. The calculated delay of VACT relative to the trailing edge of HREF can be read by the receiving end via RAM 0x10f for window 1 or 0x11f for window 2 (see section 2.6.).

Fig. 2-34: VREF timing for EVEN fields

## 2.8. Windowing the Video Field

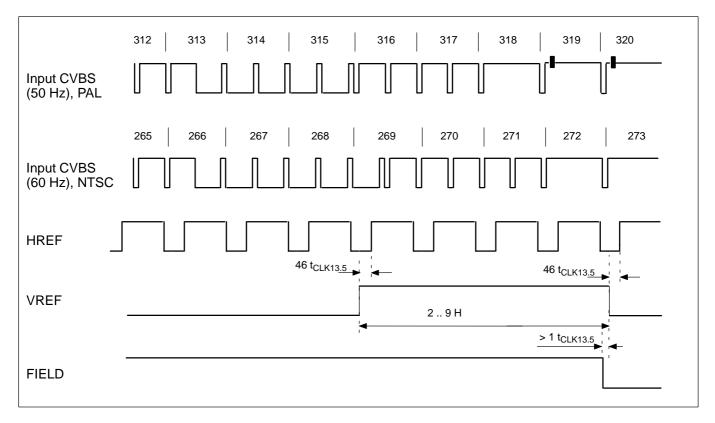

For each input video field, two non-overlapping video windows can be defined. The dimensions of these windows are supplied via I<sup>2</sup>C commands. The presence of two windows allows separate processing parameters such as filter responses and the number of pixels per line to be selected.

External control over the dimensions of the windows is performed by I<sup>2</sup>C writes to a window-load-table (Win-LoadTab). For each window, a corresponding WinLoad-Tab is defined in a table of registers in the FP-RAM [window1: 0x120–128; window2: 0x12a–132]. **Data written to these tables does not become active until the corresponding latch bit is set** in the control register FP-RAM 0x140. A 2-bit flag specifies the field polarity over which the window is active [vlinei1,2].

Vertically, as can be seen in Fig. 2–35, each window is defined by a beginning line given in FP-RAM 0x120/12A, a number of lines to be read-in (FP-RAM 0x121/12B), and a number of lines to be output (FP-RAM 0x122/12C). Each of these values is specified in units of video lines.

Fig. 2-35: Vertical dimensions of windows

The option, to separately specify the number of input lines and the number of output lines, enables vertical compression. In the VPX, vertical compression is performed via simple line dropping. A nearest neighbor algorithm selects the subset of the lines for output. The presence of a valid line is signalled by the 'video active' qualifier (or the corresponding SAV/EAV code in embedded sync modes).

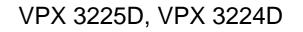

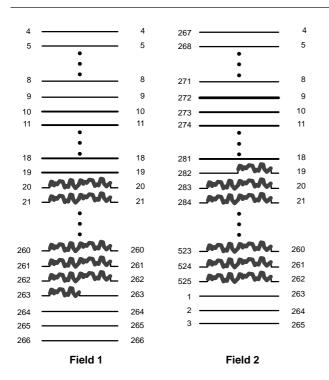

The numbering of the lines in a field of interlace video is dependent on the line standard. Figs. 2-37 and 2-38 illustrate the mapping of the window dimensions to the actual video lines. The indices on the left are the line numbers relative to the beginning of the frame. The indices on the right show the numbering used by the VPX. As seen here, the vertical boundaries of windows are defined relative to the field boundary. Spatially, the lines from field #1 are displayed above identically numbered from field #2. For example: On an interlace monitor, line #23 from field #1 is displayed directly above line #23 from field #2. There are a few restrictions to the vertical definition of the windows. Windows must not overlap vertically but can be adjacent. The first allowed line within a field is line #10 for 525/60 standards and line #7 for 625/50 standards. The number of output lines cannot be greater than the number of input lines (no vertical zooming). The combined height of the two windows cannot exceed the number of lines in the input field.

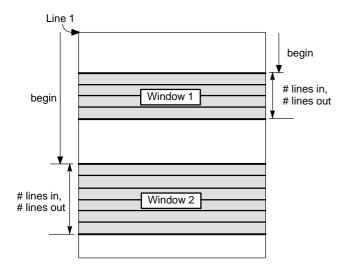

Horizontally, the windows are defined by a starting point defined in FP-RAM 0x123/12D and the length in FP-RAM 0x124/12E. They are both given relative to the number of pixels (NPix) in the active portion of the line (Fig. 2–36) selected in FP-RAM 0x125/12F. The scaling factor is calculated internally from NPix.

Fig. 2–36: Horizontal dimensions of the sampling window

Fig. 2-37: Mapping for 525/60 line systems

Fig. 2-38: Mapping for 625/50 line systems

There are some restrictions in the horizontal window definition. The total number of active pixels (NPix) must be an even number. The maximum value for NPix should be 800. Values up to 864 are possible, but for short input lines, video data is not guaranteed at the end of the line since VACT will be interrupted at the beginning of the next line. HLength should also be an even number. Obviously, the sum of HBegin and HLength may not be greater than NPix.

Window boundaries are defined by writing the dimensions into the associated WinLoadTab and then setting the corresponding latch bit in the control word FP-RAM 0x140 [latwin]. Window definition data is latched at the beginning of the next video frame. Once the WinLoad-Tab data has been latched, the latch bit in the Control word is reset. By polling the Infoword (FP-RAM 0x141), the external controller can know when the window boundary data has been read. Window definition data can be changed only once per frame. Multiple window definitions within a single frame time are ignored and can lead to error.

## 2.9. Temporal Decimation

To cope with bandwidth restrictions in a system, the VPX supports temporal dropping of video frames via suppression of the VACT signal. Dropping will be applied for video windows only. There is no influence on the state of the VBI-window. This mode can be activated for each video window by setting the enable flag in the corresponding WinLoadTab (FP-RAM 0x121/12B). The selection in FP-RAM 0x157 determines how many frames will be output within an interval of 3000 frames. Note that this selection is applied for both video windows, but decimation can be enabled for each window separately. The number of valid frames is updated only if the corresponding latch flag in FP-RAM 0x140 [lattdec] is set. Frame dropping with temporal decimation can be combined with the field disable flags (FP-RAM 0x121/12B). Within valid video frames, each field type can be disabled separately.

#### 2.10. Data Slicer

The slicer is only available on VPX 3225D. Software drivers accessing the slicer I<sup>2</sup>C registers should therefore check the VPX part number.

#### 2.10.1. Data Broadcast Systems

The existing data broadcast systems are specified by a limited set of parameters:

- line multiplex

- bit rate

- modulation

- start timing

- clock run-in (CRI)

- framing code (FRC)

- number of data bytes

| Text<br>System | TV<br>Standard | TV<br>Lines | Bitrate        | Modulation | Timing  | CRI     | FRC   | No.<br>Bytes |

|----------------|----------------|-------------|----------------|------------|---------|---------|-------|--------------|

| WST            | PAL            | 6–22        | 6.937500Mbit/s | NRZ        | 10.3 μs | '5555'x | '27'x | 42           |

| VPS            | PAL            | 16          | 2.500000Mbit/s | Bi-Phase   | 12.5 μs | '5555'x | '51'x | 13           |

| WSS            | PAL            | 23          | 0.833333Mbit/s | Bi-Phase   | 11.0 μs | '3c78'x | 'f8'x | 11           |

| Caption        | PAL            | 21          | 1.006993Mbit/s | NRZ        | 10.5 μs | 'aaa0'x | 'c2'x | 4            |

| VITC           | PAL            | 6–22        | 1.812500Mbit/s | NRZ        | 11.2 μs | ?       | ?     | 9            |

| Antiope        | SECAM          | 6–22        | 6.203125Mbit/s | NRZ        | 10.5 μs | '5555'x | 'e7'x | 37           |

| WST            | NTSC           | 10–21       | 5.727272Mbit/s | NRZ        | 9.6 μs  | '5555'x | '27'x | 34           |

| NABTS          | NTSC           | 10–21       | 5.727272Mbit/s | NRZ        | 10.5 μs | '5555'x | 'e7'x | 33           |

| Caption        | NTSC           | 21          | 0.503496Mbit/s | NRZ        | 10.5 μs | 'aaa0'x | 'c2'x | 2            |

| 2xCaption      | NTSC           | 10–21       | 1.006993Mbit/s | NRZ        | 10.5 μs | '2aa0'x | 'b7'x | 4            |

| VITC           | NTSC           | 10–21       | 1.812500Mbit/s | NRZ        | 11.2 μs | ?       | ?     | 9            |

| CGMS           | NTSC           | 20          | 0.450450Mbit/s | NRZ        | 11 µs   | '10'b   | -     | 3            |

Table 2–11: Data Broadcast Systems

# 2.10.2. Slicer Functions

Fig. 2-39: Slicer block diagram

## 2.10.2.1. Features

- 8-bit digital FBAS input

- 8-bit unbuffered ascii data output

- internal sync separation

- PAL and NTSC operation

- VBI and full-field mode

- automatic slicer adaptation

- text reception down to 30% eyeheight

- soft error correction

- simultaneous decoding of 4 different text services

- main service: programmable

- additional: VPS in line 16

- additional:

additional:

- CAPTION in line 21 WSS in line 23

- programmable text parameters for main service

- bit rate

- clock run-in

- framing code

- error tolerance

- number of data bytes

- operation controlled by I<sup>2</sup>C registers

## 2.10.2.2. Input

The slicer receives an 8-bit digitized FBAS signal which is clamped to the back porch level. The teletext signal amplitude can vary to a certain degree ( $\pm$ 3 dB), as the slicer will adapt its internal slice level.

#### 2.10.2.3. Automatic Adaptation

The slicer measures certain signal characteristics as DC offset, level, bandwith, and phase error. A digital filter at the input stage is used to compensate bandwith effects of the transmission channel. A DC shifter generates a DC free text signal even in case of co-channel interference. The internal slice level is adapted to the teletext signal level. The teletext sampling rate is generated by a phase accumulator running at 20.25 MHz, which is synchronized during framing code and clock run-in. The increment of the phase accumulator is programmable and can be used to set up any bit rate with the formula:

increment = 2048 \* bit rate/20.25 MHz

## 2.10.2.4. Standard Selection

The main teletext service can be received in VBI lines only or in every line of each field (full-field mode). All parameters needed to identify a teletext service are programmable. The slicer uses a reference of 24 bits to identify a teletext service. This reference is compared with the first received teletext bits which are often named clock run-in (CRI) and framing code (FRC). If there is a match, the slicer will start signal adaptation and write the following data to the output stage. The reference can be reduced in length by setting a mask for services which do not have a 16-bit clock run-in. Bit errors can be allowed by setting a tolerance level for every byte of the reference. Additionally, the slicer can switch to other teletext services during dedicated lines of the VBI. These can be line 16 for VPS, line 21 for CAPTION, or line 23 for WSS. In this case, the parameters will be hard wired.

## 2.10.2.5. Output

The slicer delivers a synchronous burst of decoded teletext data bytes together with a data valid signal. This data stream is fed into the video FIFO of the VPX backend. The data rate depends on the teletext bit rate (divided by 8), the length of the burst is programmable. The burst can optionally be extended to 64 bytes independently of the selected teletext service (fill64 mode). The dummy bytes needed to fill the burst to 64 bytes are delivered at a rate of 20.25 MHz. Normally, there is no output during lines without text transmission or unknown text signals. For some applications, it is necessary to have constant memory mapping. Therefore, the slicer can be forced to output 64 bytes per line even if no text is detected (dump mode).

The first 3 bytes of the data burst carry information to identify the received teletext service. The 2 byte line number contains a free running frame counter which can be used to identify data loss in the framebuffer of a capture application. The field bit can be used to identify field dependent services such as CAPTION. The 10-bit line number corresponds to the standard line counting scheme of a PAL composite video signal; in case of NTSC, the value "3" is subtracted.

The number of useful data bytes at the output is programmable and should be set accordingly to the selected teletext standard. To get "n" data bytes, the value "n+1" has to be programmed, because of the additional framing code byte.

In case of dump mode, byte numbers "1" and "2" are also valid for lines without detected text data. They are then followed by 62 dummy bytes.

| Table 2-12: Slicer Pro | ogramming |

|------------------------|-----------|

|------------------------|-----------|

| Programmable<br>Parameter | WST<br>Setup | CAPTION<br>Setup |

|---------------------------|--------------|------------------|

| TV standard               | pal          | ntsc             |

| full field                | off          | off              |

| increment                 | 702          | 153              |

| reference                 | 27 55 55     | c2 aa a0         |

| mask                      | 00 00 03     | 00 00 Of         |

| error tolerance           | 01 01 01     | 01 01 00         |

| data length               | 43           | 4                |

| dummy mode                | on           | on               |

| dump every line           | off          | on               |

#### Table 2–13: Slicer Output Format

| Byte<br>Number    | Byte<br>Format      | Bit<br>Format                                                     |

|-------------------|---------------------|-------------------------------------------------------------------|

| 1                 | line number<br>high | b[7:3] frame counter<br>b[2] odd field<br>b[1:0] line number[9:8] |

| 2                 | line number<br>low  | b[7:0] line number[7:0]                                           |

| 3                 | framing code        | b[7:0] as transmitted                                             |

| 4                 | 1st data byte       | b[7:0] as transmitted                                             |

| •                 |                     |                                                                   |

| program-<br>mable | last data byte      | b[7:0] as transmitted                                             |

|                   | dummy byte          | b[7:0] 00000000                                                   |

|                   |                     |                                                                   |

| 64                | dummy byte          | b[7:0] 00000000                                                   |

#### 2.11. VBI Data Acquisition

The VPX supports two different data acquisition modes for the vertical blanking interval: a bypass mode for raw data of the vertical blanking interval and a data slicer mode in which dedicated hardware provides constant packets of sliced VBI-data. The data packets have a default size of 64 bytes. Dependent on the bit slicer frequency, smaller packet sizes can be selected via FP-RAM 0x139.

For both services, the start and end line of a vertical blanking interval (VBI) window can be defined for each field with FP-RAM 0x134–137. Teletext data can occur between lines 6 and 21 of each field. However, the VBI-window is freely programmable. It is possible to select the whole field (beginning with line #3). If video windows are enabled, the VBI-window should end two lines before the first valid line of the next video window. The VBI-window can be activated via bit[0] in FP-RAM 0x138. The selection of the acquisition mode is done with bit[1].

The identification of valid VBI-lines is possible with the VACT-signal (or the 'active line'-flags in the modes with embedded syncs) or a special 'data active' signal on the

TDO pin. Bit[10] of FP-RAM 0x154 selects between these two cases. In the default mode, VACT is used. The output of both signals can be suppressed optionally with bit[2] of FP-RAM 0x138. In this case, the graphic controller has to use only the HREF signal to mask the active video data.

In the ITU-R656 mode, VBI-data can be transmitted as vertical ancillary data (with 7 bit resolution + odd parity). The selections for the VBI-window will be updated by setting bit[11] in FP-RAM 0x138.

## 2.11.1. Raw Teletext Data

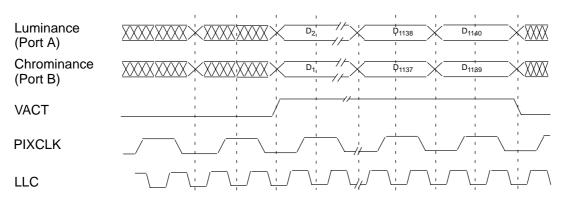

During lines within the VBI-window, specified by the user settings in the corresponding Load-Table, the VPX internally acquires 1140 raw data bytes of the luminance input at a rate of 20.25 MHz corresponding to 56.296  $\mu$ s of the analog video. Chrominance data is not valid. The raw data samples are demultiplexed internally to 570x16 bit on the luminance and chrominance port. The external timing corresponds to the video mode with 570 output samples for an uncropped window. Figure 2–41 shows the timing of both data ports and the necessary reference signals in this mode.

Fig. 2-40: Horizontal dimensions of the window for raw VBI-data

Fig. 2-41: Timing during lines with raw VBI-data (single clock)

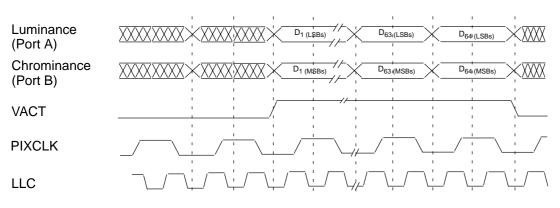

# 2.11.2. Sliced VBI Data

The data acquisition of the hardware slicer is completely independent from the video front-end. The slicer provides data packets of a constant size (filled with dummy bytes). The data packets have a default size of 64 bytes. Depending on the bit slicer frequency, smaller packet sizes can be selected via FP-RAM 0x139.

The FP switches into the slicer mode within the vertical blanking interval defined by the user settings in the 'Load-Table' for the VBI-window. The 8-bit slicer data supplies sliced data bits of the luminance input. Chrominance data is not valid. Since in the 8-bit output modes (ITU-R656, BStream), the values 0.254 and 255 are protected, each slicer sample is separated into two nibbles for transmission. Table 2–14 shows the implemented data formats.

In each path, one nibble is transmitted twice. The LSB is inverted for odd parity. This assures that the values 0 and 255 will not occur (for the detection of embedded syncs). In the mode with embedded timing event codes, chrominance data will be limited additionally. No significant information will be lost since only Bit 0 and 1 will be modified. Figure 2–42 shows the timing of data and reference signals in this mode.

**Table 2–14:** Splitting of sliced data to luminance and chrominance output

| Word                       | MSE | 3  |    | Bit | No. |    |    | LSB       |

|----------------------------|-----|----|----|-----|-----|----|----|-----------|

|                            | 7   | 6  | 5  | 4   | 3   | 2  | 1  | 0         |

| Slicer<br>Data             | S7  | S6 | S5 | S4  | S3  | S2 | S1 | S0        |

| Chromi-<br>nance<br>Output | S7  | S6 | S5 | S4  | S7  | S6 | S5 | not<br>S4 |

| Lumi-<br>nance<br>Output   | S3  | S2 | S1 | S0  | S3  | S2 | S1 | not<br>S0 |

The splitting described above can be disabled by setting bit 6 in the 'format\_select' register. In this case, the sliced samples will be transmitted in the luminance path only. To avoid modification of valid data, the limitation of luminance data in the 8-bit output modes should be suppressed with bit 8 in the same register (note that luminance codes will not be protected).

Fig. 2-42: Timing during lines with sliced VBI-data (single clock)

#### 2.12. Operational Modes

The relationship between the video timing signals (HREF and VREF) and the analog input video is determined by the selected operational mode. Three such modes are available: the **Open Mode**, the **Forced Mode**, and the **Scan Mode**. These modes are selected via I<sup>2</sup>C commands [FP-RAM 0x140, settm, lattm].

#### 2.12.1. Open Mode

In the Open Mode, both the HREF and the VREF signal track the analog video input. In the case of a change in the line standard (i.e. switching between the video input ports), HREF and VREF automatically synchronize to the new input. When no video is present, both HREF and VREF float to the idling frequency of their respective PLLs. During changes in the video input (drop-out, switching between inputs), the performance of the HREF and VREF signals is not guaranteed.

#### 2.12.2. Forced Mode

In the Forced Mode, VREF and HREF follow the input video signal within certain tolerances. Dedicated hardware is used to monitor the frequency of the analog timing. At the moment when the video signal exceeds the allowed timing tolerances, generation of the timing signals is taken over by free running hardware. If the input video is still present, the VPX continually attempts to resynchronize to it.

For each of the two video line standards (625/50 and 525/60), there exist normative values for the period of both the HREF and VREF signals. Many analog input signals deviate significantly from these norms (example: consumer VCRs in their shuttle modes). In the Forced Mode, monitoring hardware is used to impose an upper boundary on the deviation. The maximum allowed horizontal deviation is  $\pm 24 \ \mu$ s. The upper boundary for vertical deviation is  $\pm 11\%$  of the number of lines in the selected line standard (625/50:  $\pm 35$  lines, 525/60:  $\pm 30$  lines)

#### 2.12.3. Scan Mode

In the Scan Mode, the HREF and VREF signals are always generated by free running hardware. They are therefore completely decoupled from the analog input. The output video data is always suppressed.

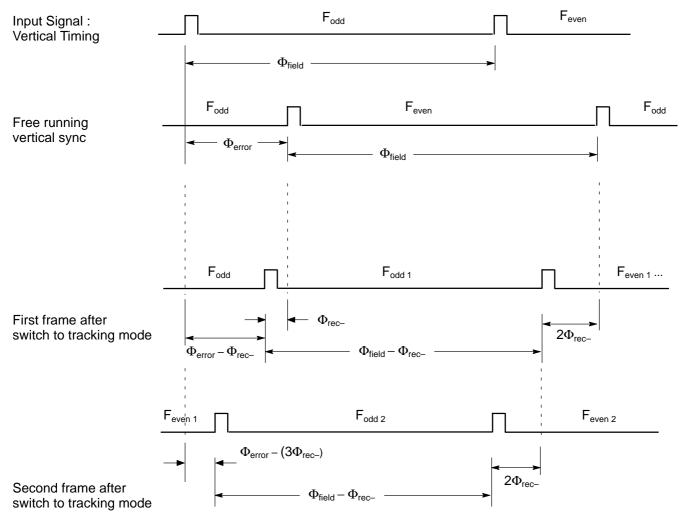

The purpose of the Scan Mode is to allow the external controller to freely switch between the analog inputs while searching for the presence of a video signal. Information regarding the video (standard, source, etc...) can be queried via  $l^2C$  read.